### Non-Volatility For Ultra-Low Power Asynchronous Circuits in Hybrid CMOS/Magnetic Technology

Eldar Zianbetov<sup>1</sup>, Edith Beigne<sup>2</sup>, Gregory Di Pendina<sup>3</sup>

<sup>1</sup> CEA, INAC-SPINTEC, F-38000, Grenoble, France

<sup>2</sup> CEA, DACLE, F-38000, Grenoble, France

<sup>3</sup> CNRS, SPINTEC, F-38000, Grenoble, France

- Motivation & Background

- Non-Volatile C-element

- Asynchronous Non-Volatile circuits

- Summary & Conclusion

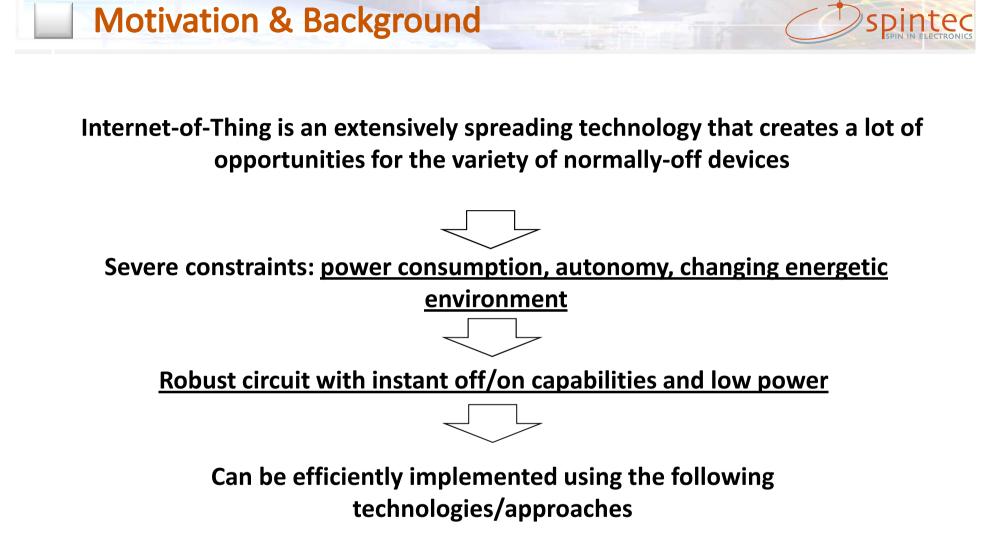

**Motivation & Background**

Internet-of-Thing is an extensively spreading technology that creates a lot of opportunities for the variety of normally-off devices

Zero consumption in offline mode

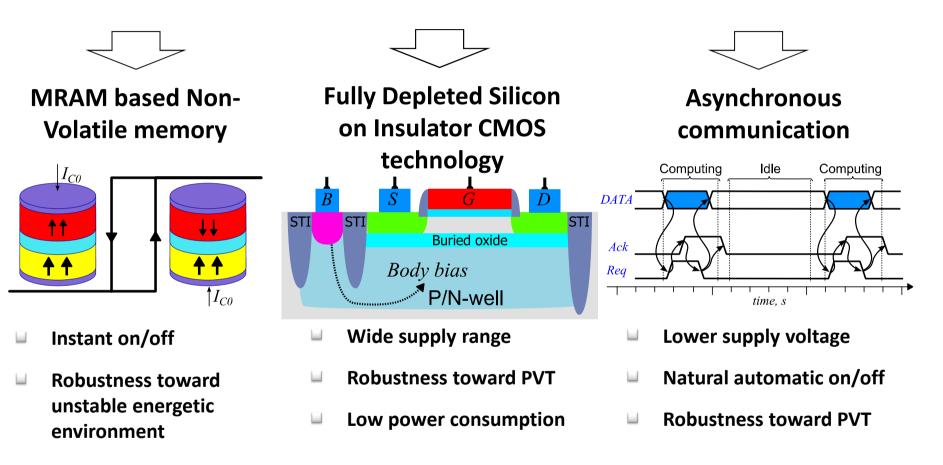

# Background: Logic-in-Memory & Integration

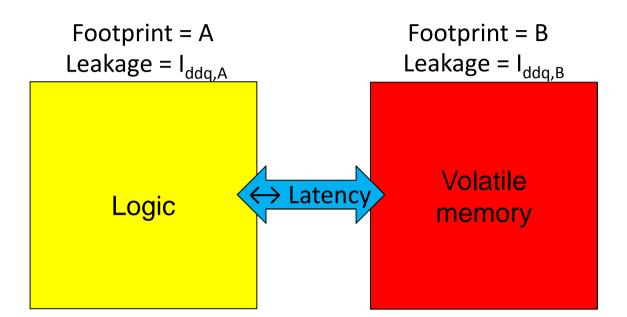

Von Neumann architecture:

- Large footprint (A + B)

- High dynamic & static losses

- Latency

- Complex layout

spintec

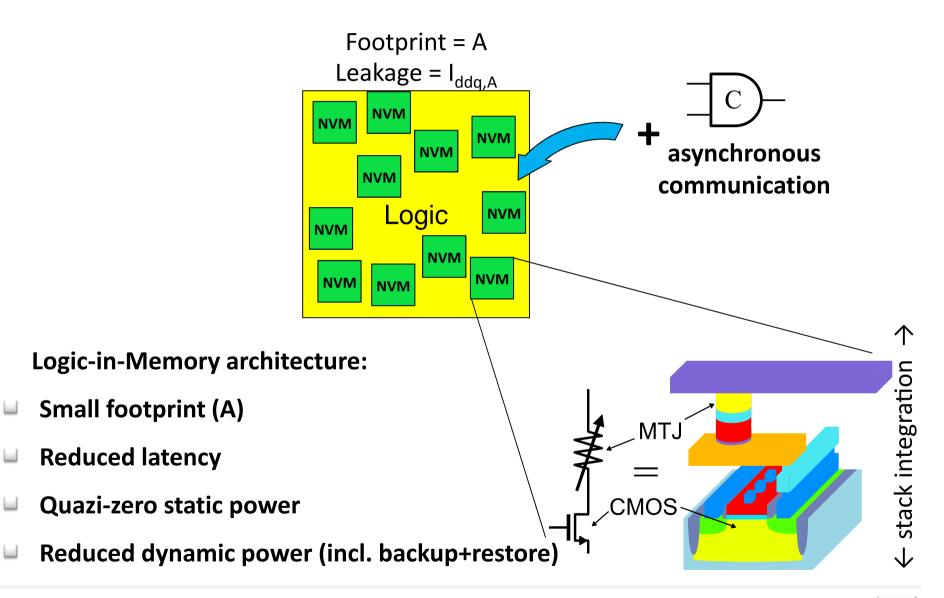

# Background: Logic-in-Memory & Integration

spintec

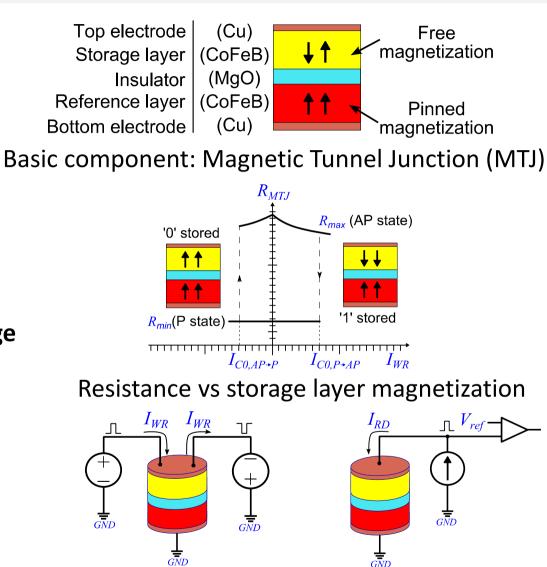

#### Background: Magnetic memory (STT-MRAM)

#### Why magnetic memory?

- Non-volatile: no leakage

- Fast R/W: ns range

- High endurance: > 10 years

- Low R/W energy : tens of fJ range

- Low R/W voltage: < 500 mV</p>

- Easy to embed: e.g. in BEOL

- High density: < 40 nm</p>

Write '0'

Write '1'

ASYNC 2015 - 06/05/2015

Read

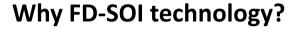

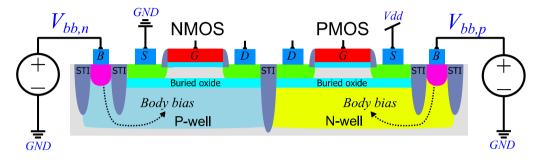

# **Background: FD-SOI technology**

- High performance/lower power

- Low variability

- Advanced power/speed

- control features

#### Cross section view of FD-SOI transistors

spintec

# Outline

#### Motivation & Background

#### Non-Volatile C-element

- Asynchronous Non-Volatile circuits

- Summary & Conclusion

spintec

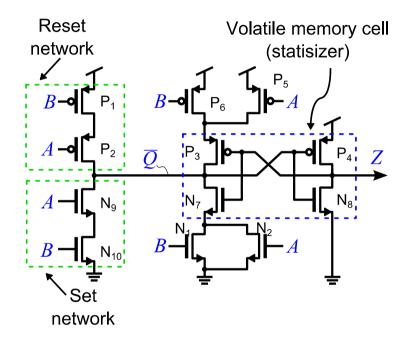

#### Non-volatile C-element: schematic

#### Conventional volatile C-element (Muller gate)

#### state is lost @ power gating !

#### Proposed non-volatile cell

- + 2MTJ for differential NVM

- + 4T for read procedure

- + 1T for write procedure

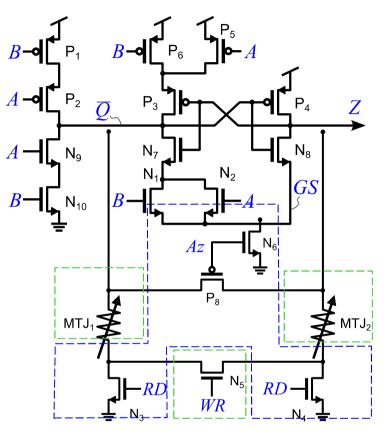

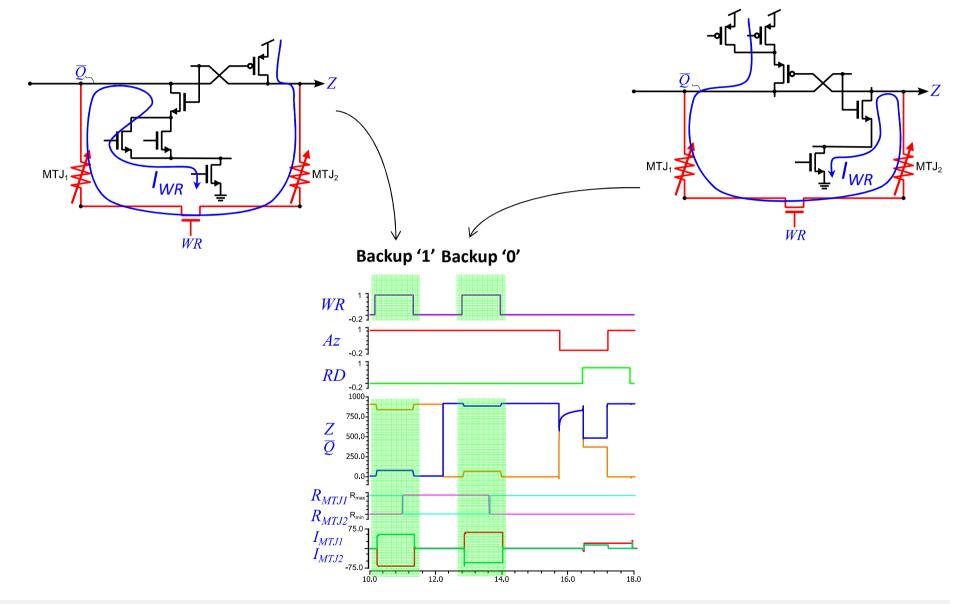

### Non-volatile C-element: write principle

### Non-volatile C-element: read principle

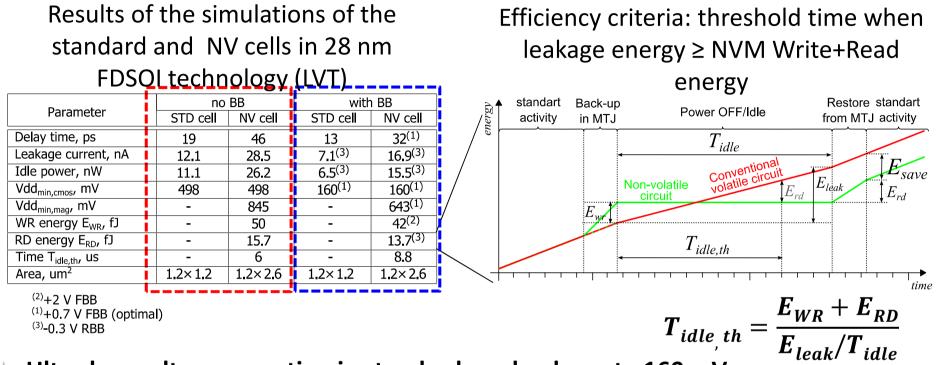

Non-volatile C-element: energy efficiency

- Ultra-low voltage operation in standard mode: down to 160 mV

- Low voltage operation in NV mode: 30% lower than nominal supply

- Body Bias reduces the cost of NV feature: roughly by 15%

- NV upgrade is reasonable if idle periods are longer than 10 us

- Gate delay penalty is x2 and not an issue for the autonomous application

# Outline

- Motivation & Background

- Non-Volatile C-element

- Asynchronous Non-Volatile circuits

- Summary & Conclusion

spintec

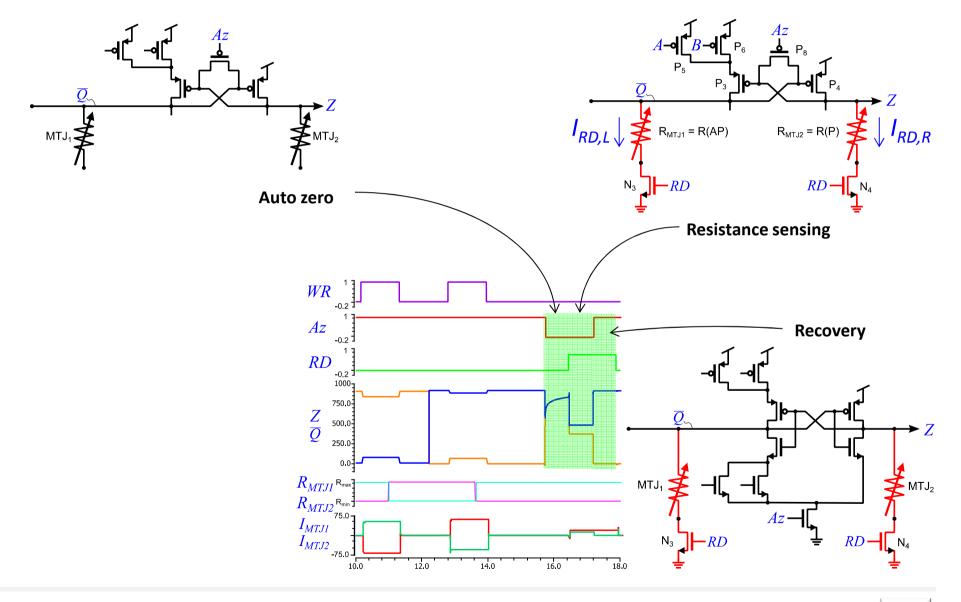

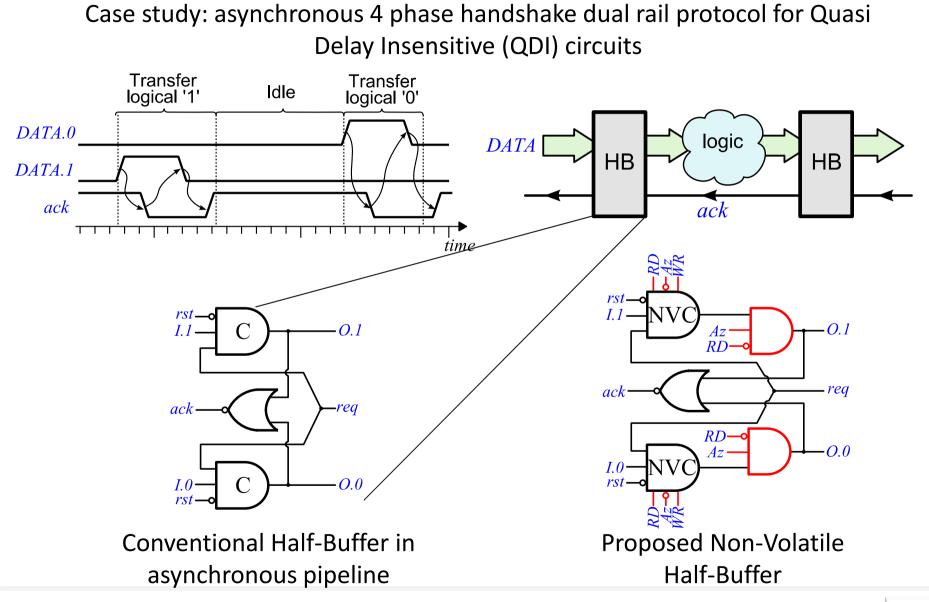

### **Asynchronous NV circuits: Half-Buffer**

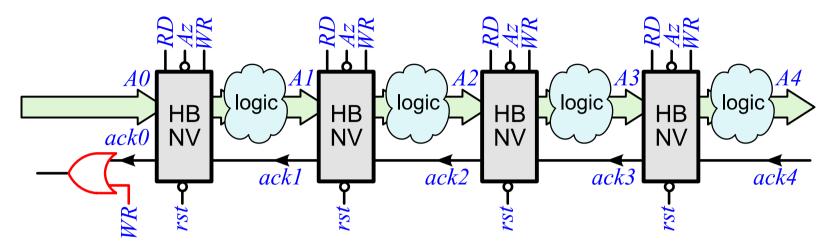

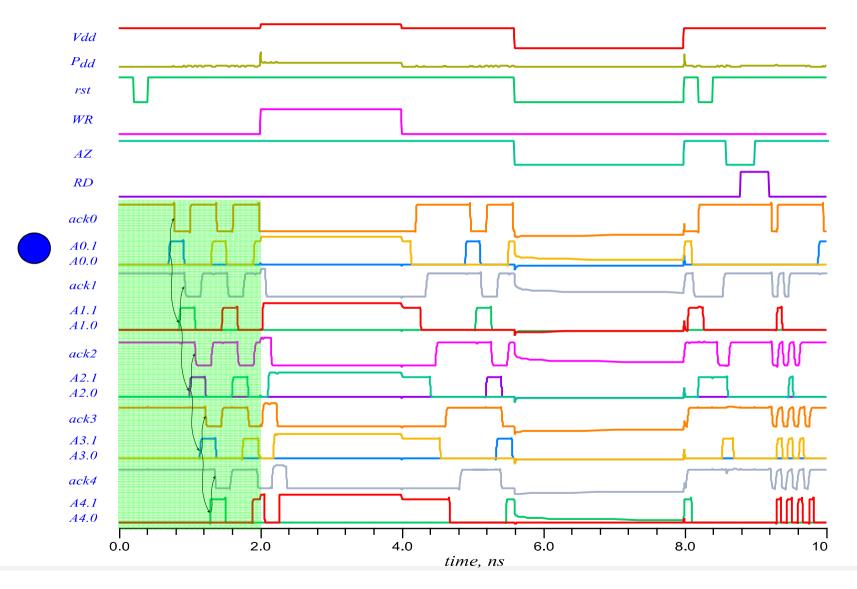

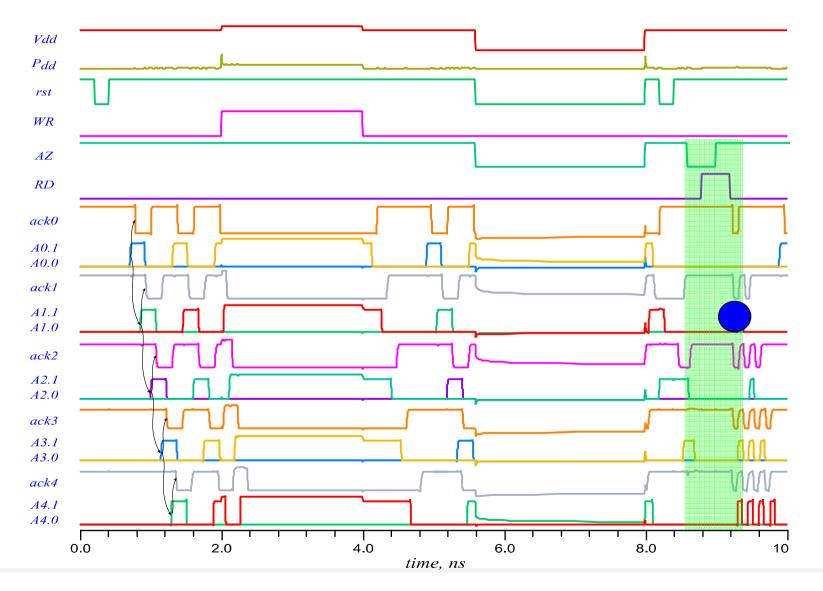

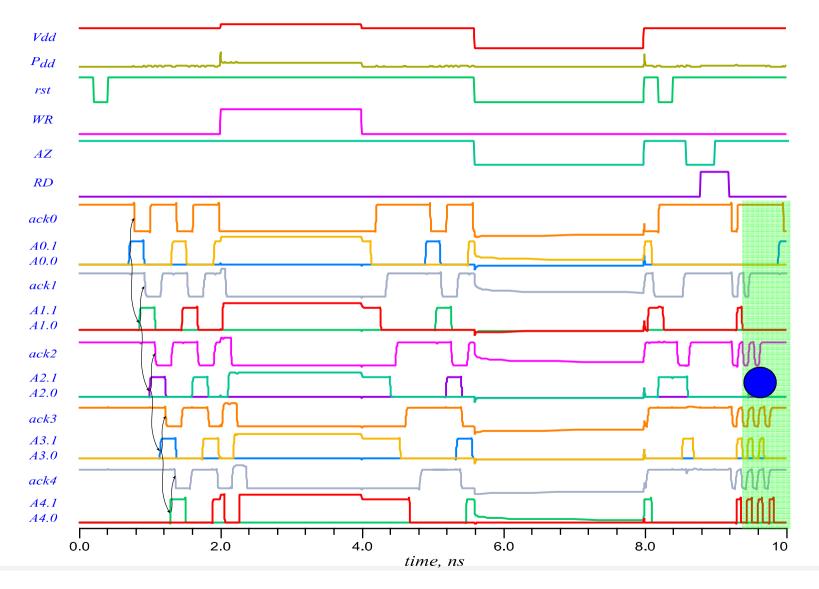

### Asynchronous NV circuits: pipeline

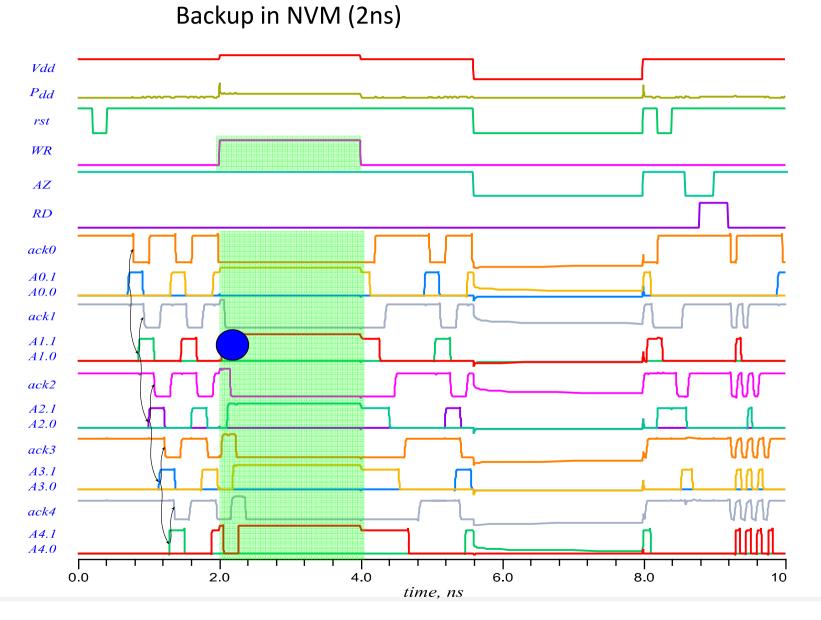

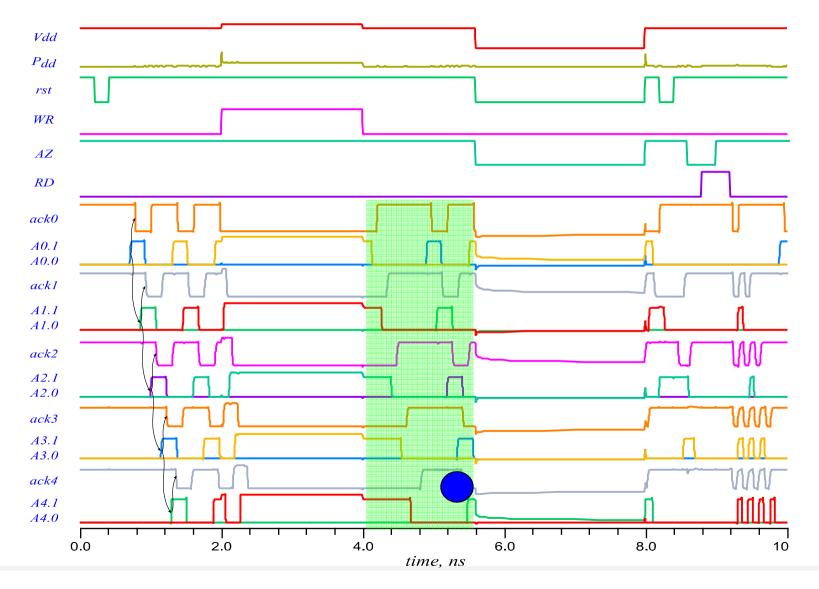

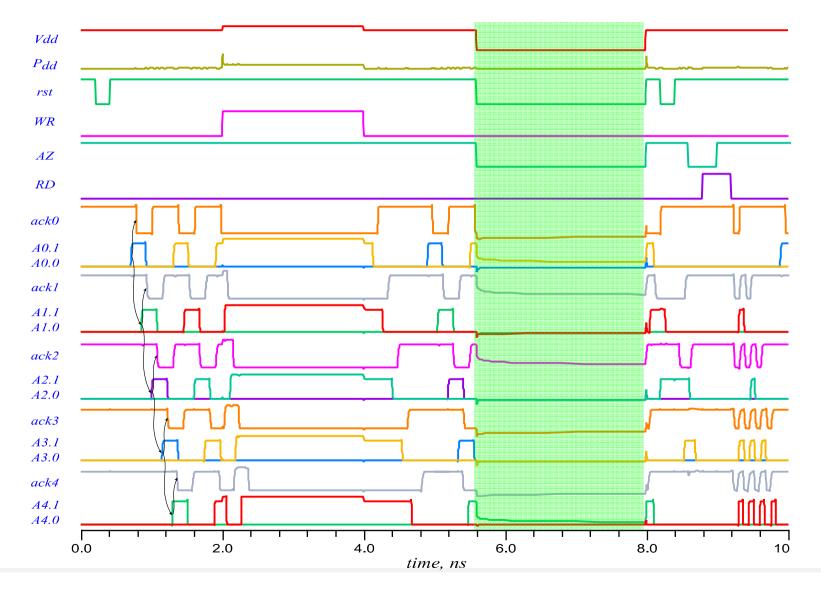

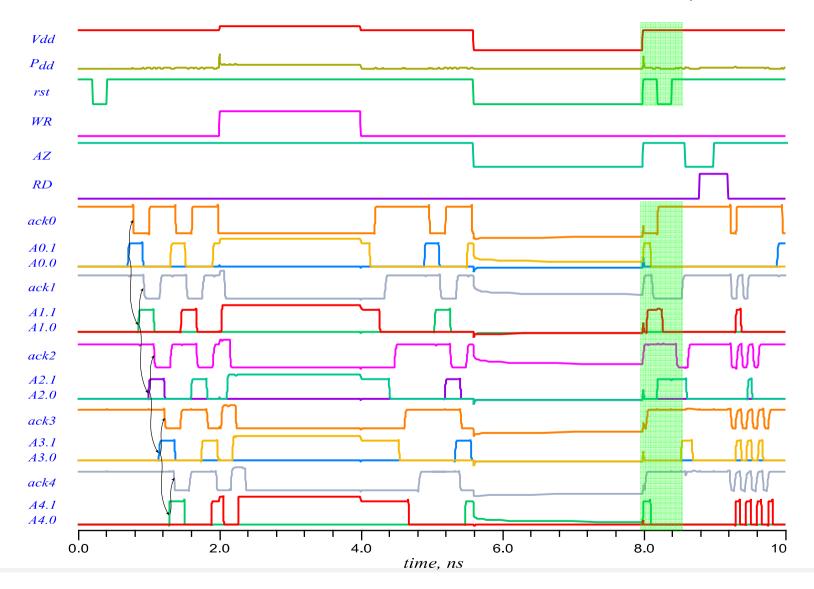

**Issues of NV implementation:**

- Synchronization of backup/restore with basic asynchronous operation of HB

- STT-MRAM writing time is significant comparing to data hold time (1-2 orders) Proposed algorithm:

- Freeze the pipeline by gating the acknowledgment signal(s) (ack  $\rightarrow$  '1')

- Keep the freeze state for a time, sufficient for the writing in NVM (e.g. T<sub>wr</sub> > 10ns)

- Release the acknowledgment signal and continue normal operation

#### Std operation mode

Continue std operation

Power off (Vdd=0V)

Power up

**Recovery from NVM**

#### Resume std operation

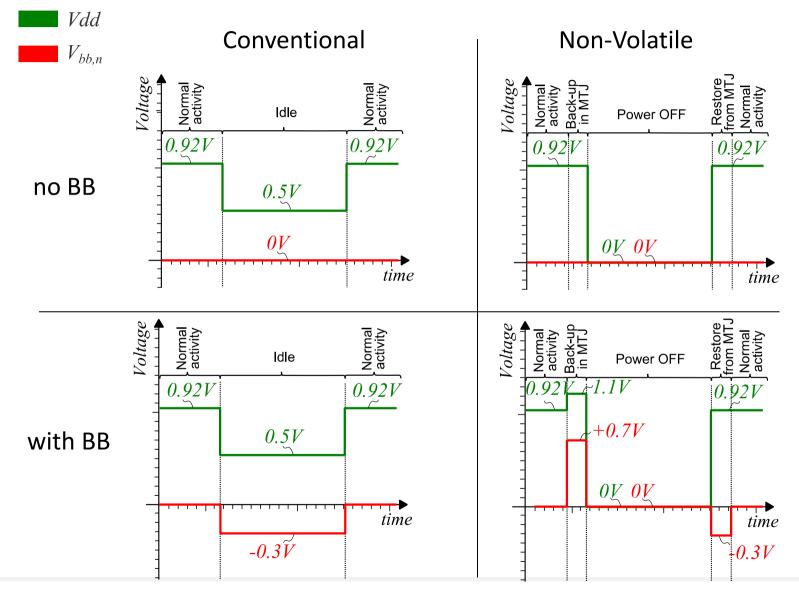

### Asynchronous NV circuits: BB and supply control spintec

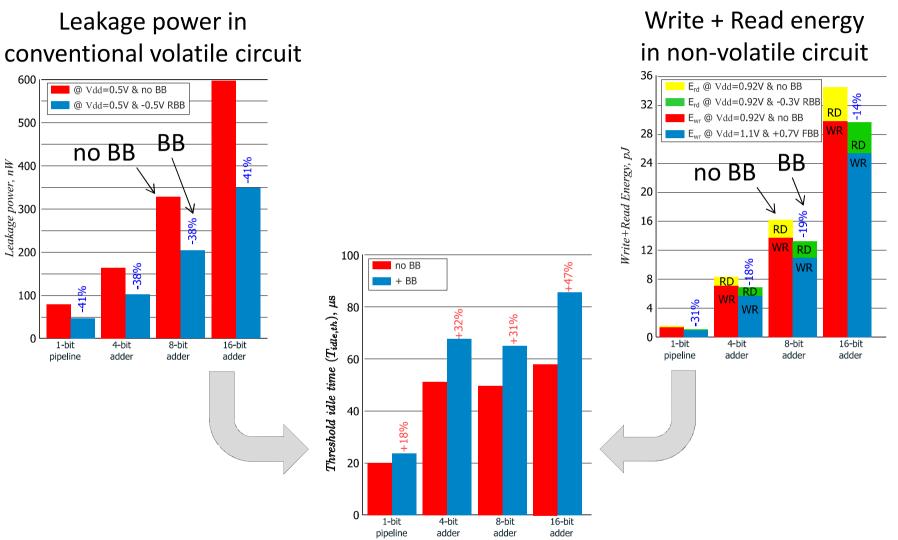

## Asynchronous NV circuits: V vs NV tradeoff

Volatile vs Non-Volatile tradeoff. NV functionality is reasonable if the idle time of the volatile circuit is greater than threshold time  $T_{idle,th}$

#### **Summary & Conclusion**

- Magnetic memory brings non-volatility to asynchronous circuits for low-power and normally-off circuits of the Internet-of-Things applications:

- The NV functionality is justified if the idle mode of the application is greater than few <u>tens of microseconds</u>

- Delay penalty (>x2) of the NV cells due to the NV functionality is too high and requires optimizations

- Adaptive control over supply and body bias voltages can minimize the power consumption during dynamic operation, idle phases and backup:

- Aggressive FBB permits to reduce the supply voltage in conventional mode down to <u>160 mV</u> and in NV mode down to <u>643 mV</u>

- Optimal FBB can save from <u>14</u> to <u>30%</u> of the energy during backup/restore

- The RBB reduces the leakage current in all simulated circuits by <u>40%</u>

#### **Future work**

- Circuit level optimizations: e.g. gate delay minimization

- Study self-adjusting solutions for minimum energy/delay

- Fine grain writing of the NVM using activity detection mechanism

# Thank you for your attention

www.spintec.fr

email: Eldar.Zianbetov@cea.fr

\* Questions are guaranteed in life; answers aren't.

ASYNC 2015 - 06/05/2015

leti