ASYNC 2015 - Fresh Ideas

## **Asynchronous Design for Harsh Environments**

Jeremy Lopes<sup>124</sup>, Gregory Di Pendina<sup>1</sup>, Edith Beigne<sup>3</sup> and Lionel Torres<sup>4</sup>

<sup>1</sup>Univ. Grenoble Alpes, CNRS, CEA INAC-SPINTEC, Grenoble, France <sup>2</sup>CNES, Service Environnement et Composants nouveaux DCT/AQ/EC <sup>3</sup>CEA LETI, Minatec, Grenoble, France <sup>4</sup>LIRMM, UMR CNRS 5506, University of Montpellier, France

**CONFIDENTIAL**

Introduction

**Simulation methodology**

**Simulation results**

#### Introduction

- Simulation methodology

- **Simulation results**

- **Conclusion and Perspectives**

### **Radiation induced particles**

Solar Flare

**Energies from** keV to 100MeV

exchange n+1

#### **Radiation induced particles**

Solar wind

Coronal mass ejection

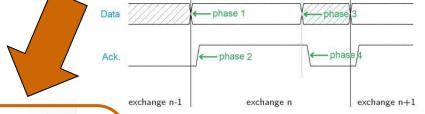

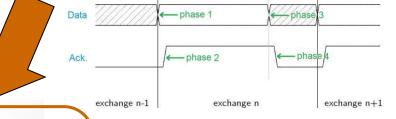

**Asynchronous Communication**

exchange n

Acknowledgement

circuits

## **Radiation induced particles**

**Energies from** keV to 100MeV

Solar wind

## **Asynchronous Communication**

Increase radiation robustness for Non-Volatile circuits

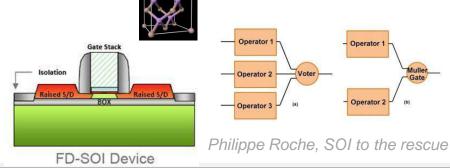

## **Radiation Hardening Techniques/Process**

# **Radiation induced particles**

## Solar wind

**Asynchronous Communication**

**Energies from** keV to 100MeV

Solar Flare

Reference laver

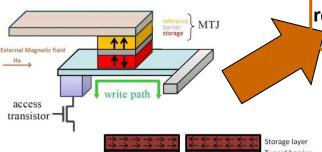

#### **Non-Volatile Memory**

Increase radiation robustness for Non-Volatile circuits

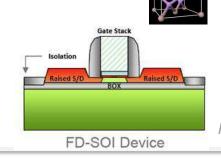

**Radiation Hardening Techniques/Process**

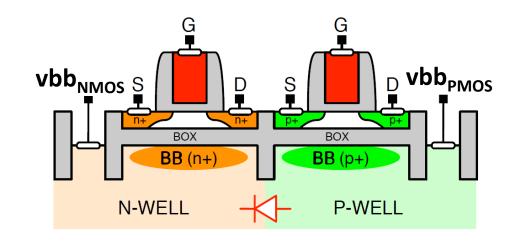

Philippe Roche, SOI to the rescue

Harold Hughes, Radiation studies of spin-transfer torque materials and devices

Parallel (R<sub>p</sub>)

Anti-parallel (Rap)

Introduction

**Simulation methodology**

Simulation results

## Simulation methodology: Simulated circuits

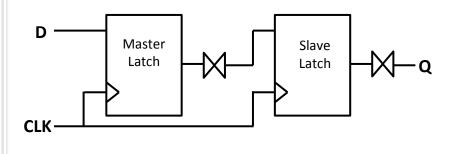

## **Synchronous**

Flip-Flop = Master latch & Slave latch

- 26 transistors

- 15 sensitive nodes

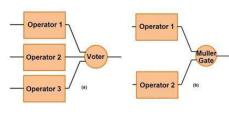

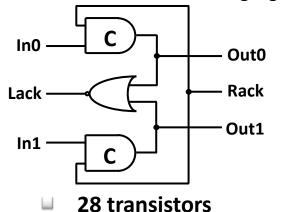

#### **Asynchronous**

Half-Buffer = 2 Muller cells & 1 logic gate

- 14 sensitive nodes

- Identical timing through transistor sizing

| Circuit type       | Number of Errors |

|--------------------|------------------|

| Flip-Flop          | 0.41             |

| NV STT Flip-Flop   | 0.47             |

| NV SOT Flip-Flop   | 0.43             |

| Half-Buffer        | 0.35             |

| NV STT Half-Buffer | 0.82             |

| NV SOT Half-Buffer | 0.66             |

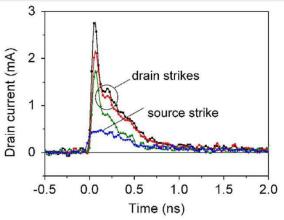

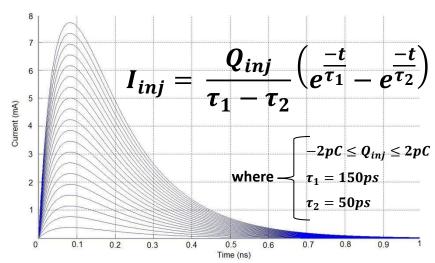

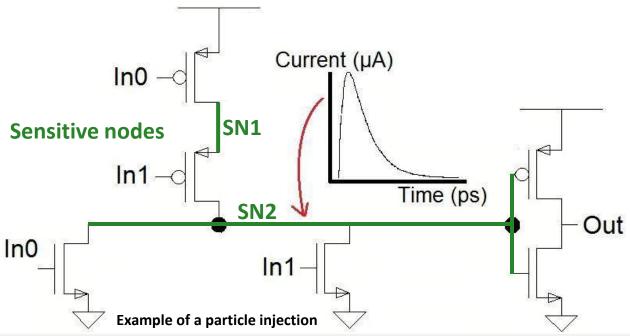

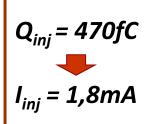

## Simulation methodology: Particle injection

Ferlet-Cavrois, V and Paillet, P and Gaillardin, and others, Statistical analysis of the charge collected in SOI and bulk devices under heavy lon and proton irradiation implications for digital SETs, Nuclear Science, IEEE Transactions on, 2006, vol. 53, no 6, pp. 3242-3252.

**CONFIDENTIAL**

Introduction

Simulation methodology

**Simulation results**

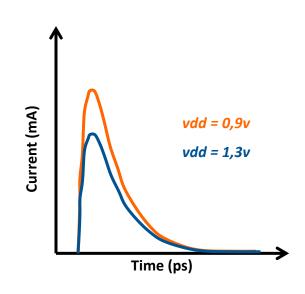

## Simulation results: Influence of the supply voltage

#### **Observations:**

As the supply voltage increases, the amplitude of the induced pulse decreases.

#### **Explanation:**

As the supply voltage increases the conductance of the transistors increases also.

#### **Conclusion:**

Use the highest supply voltage permitted by the technology for increasing the robustness toward radiation.

## Simulation results: Impact of the threshold voltage

#### **Observations:**

LVT transistors are more robust than RVT transistors.

#### **Explanation:**

LVT transistors have a higher leakage than RVT, so the induced current pulses are evacuated quicker due to the lower resistance.

#### **Conclusion:**

Use LVT transistors for space applications.

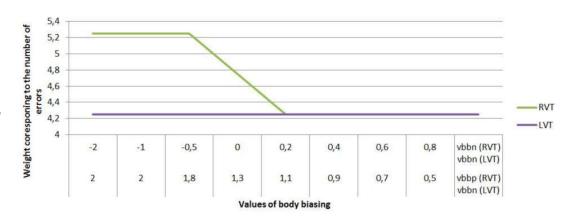

## Simulation results: Influence of body biasing

#### **Observations:**

**RVT transistors:** The number of errors decreased as vbb increased.

LVT transistors: vbb has no effect on the number of errors.

#### **Explanation:**

As vbb increases in RVT transistors, there response is boosted and the accumulated charges caused by particle strikes can be evacuated quicker.

LVT already have a low vt so the accumulated vt can be evacuated quicker.

#### **Conclusion:**

Body biasing has no effect on hardening when using LVT transistors.

Introduction

Simulation methodology

**Simulation results**

## **Conclusion and Perspectives**

#### Total Number of simulations $\approx 2000$

(Number of input combinations  $\times$  Number of Sensitive Nodes  $\times$  2 = Number of simulations)

The simulation results have demonstrated that using the highest supply voltage permitted by the technology, in conjunction with LVT transistors is the best option to harden systems at transistor level.

#### **Next Steps:**

- Comparison of Synchronous and Asynchronous architectures in a pipeline

- **Integration of MTJs in both Synchronous and Asynchronous**

- Hardening by design (TMR, DMR)

- **Architecture level studies**

## Thank you for your attention!

jeremy.lopes@cea.fr