2015 Symposium on Asynchronous Circuits and Systems

# A Pausible Bisynchronous FIFO for GALS Systems

Ben Keller\*<sup>†</sup>, Matthew Fojtik\*, Brucek Khailany\*

\*NVIDIA Corporation <sup>†</sup>University of California, Berkeley

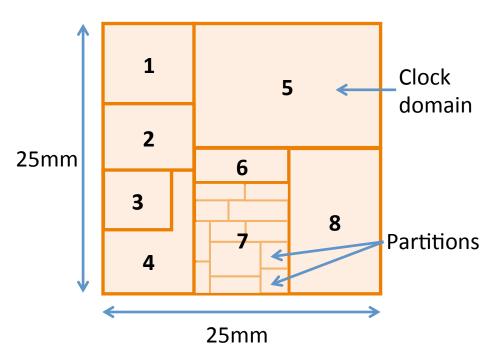

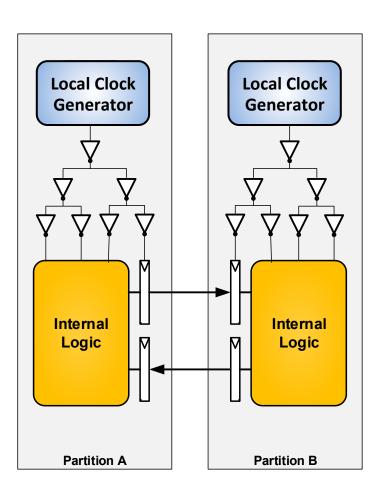

## The Nightmare of Global Clocking

- Large chips have only a handful of clock domains

- Each clock domain is many mm<sup>2</sup>, even in ≤28nm

- Made up of many partitions

Tapeout signoff currently requires distributing balanced synchronous clocks to every flip-flop in a clock domain...

- ...then closing SETUP and HOLD on all paths in the clock domain

- Across dozens of PVT corners!

## Globally Asynchronous, Locally Synchronous!

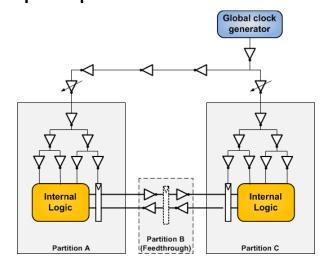

From this...

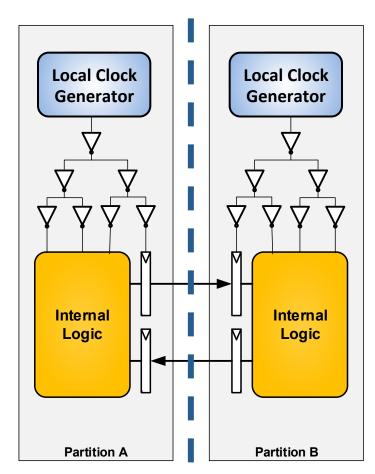

## Globally Asynchronous, Locally Synchronous!

...to this.

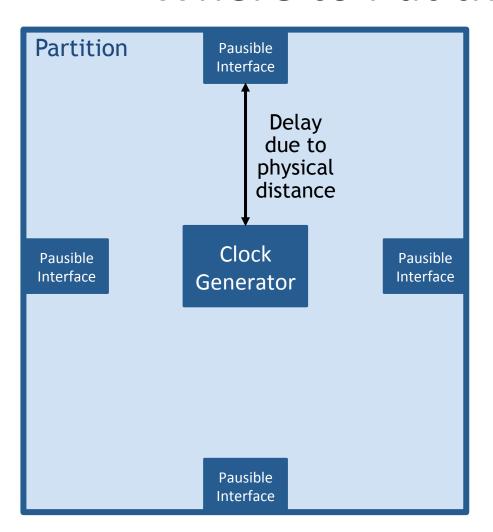

## Towards Fine-Grained GALS

**Clock Domain Crossing**

- No global clock! Local ring oscillator generates clock in each partition

- No global timing closure

- Reduce timing margin

- Tracks local PVT variation

- May improve tracking of high-frequency noise

- But there's a catch...

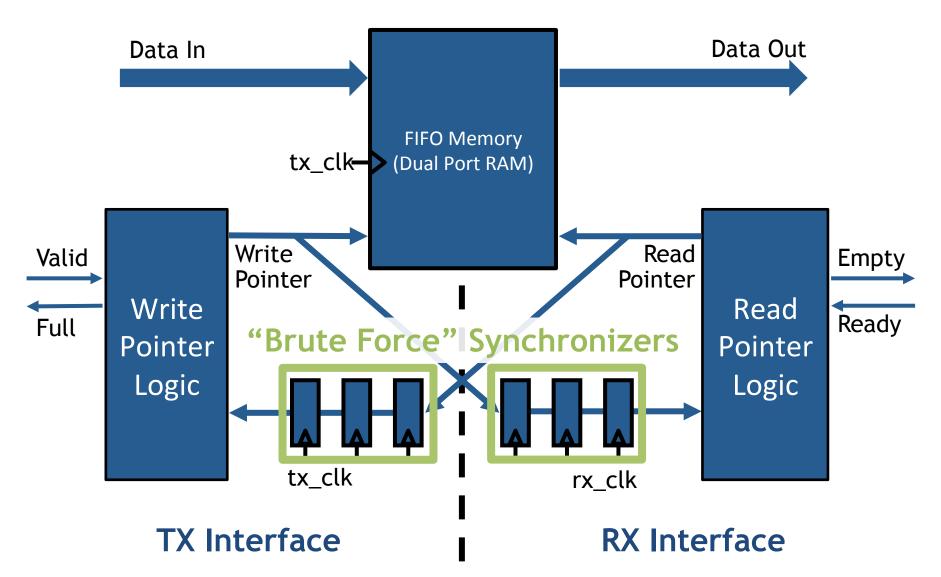

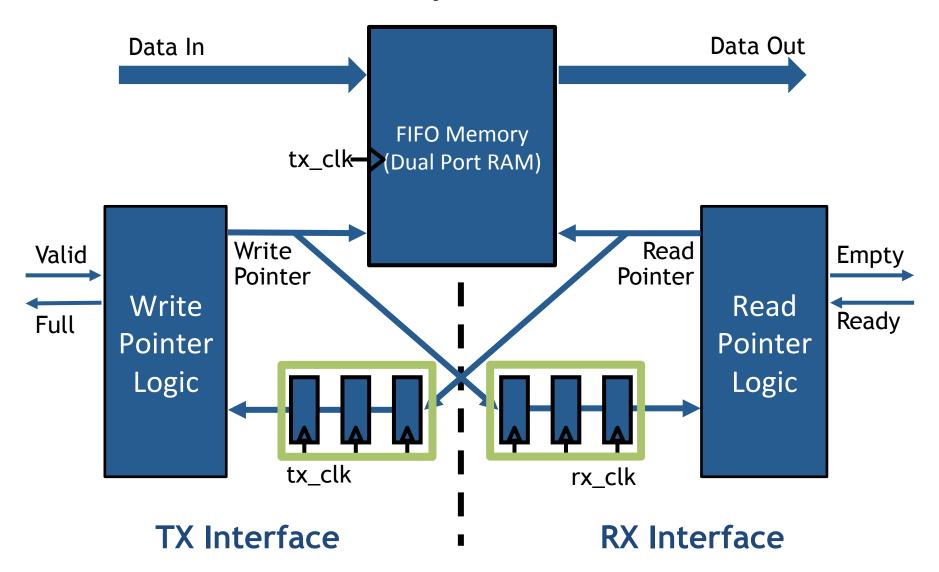

## Textbook Approach: Bisynchronous FIFO

## The Brute Force Synchronizer

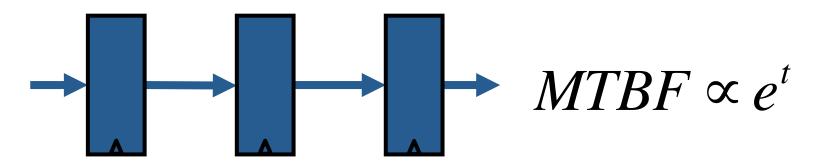

- Add latency until metastability is most likely resolved

- +3 cycles of latency at every partition boundary!

- Need to do better...

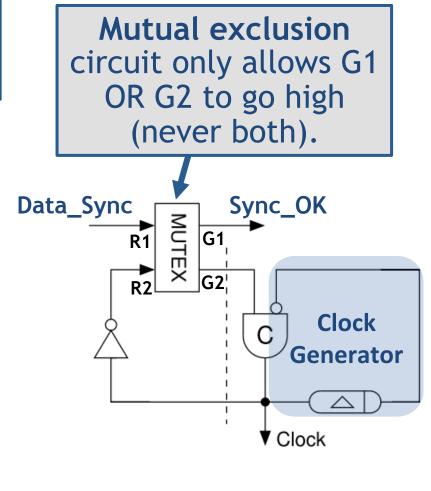

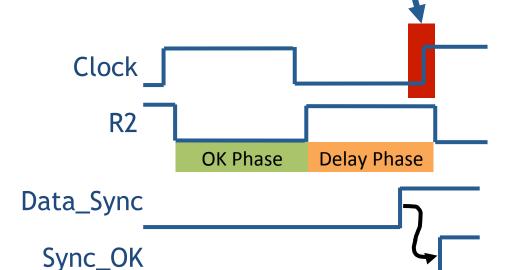

## Pausible Clocking Basics

Metastability happens when Data\_Sync transitions near the clock edge. Clock R2 **Delay Phase OK Phase** Data\_Sync Sync\_OK If data arrives when clock is high, let it through.

## Pausible Clocking Basics

Metastability happens when Data\_Sync transitions near the clock edge.

If data arrives when clock is low, delay it until after the clock edge.

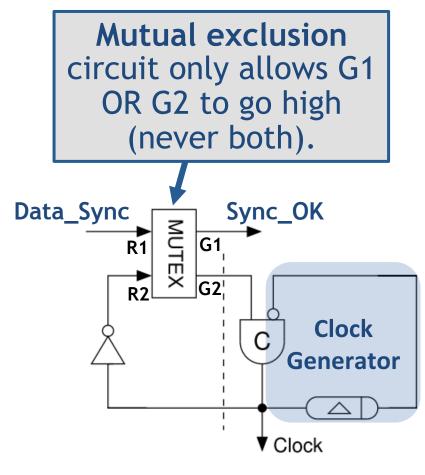

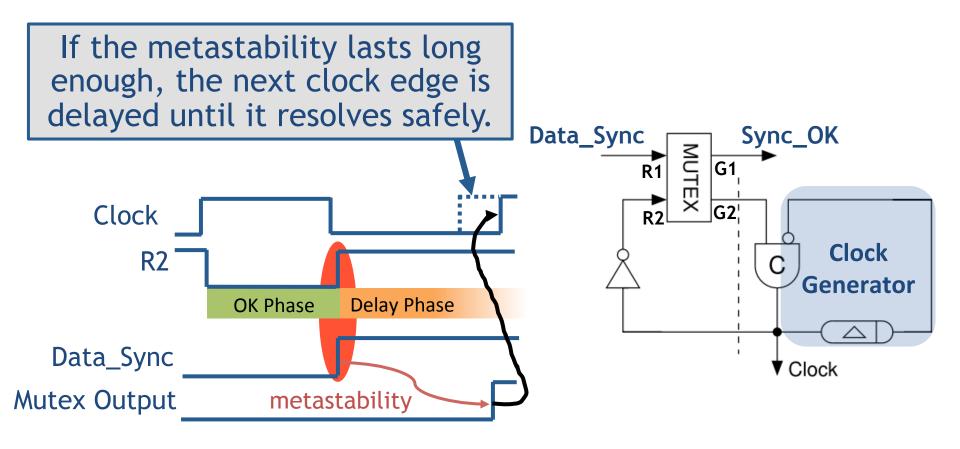

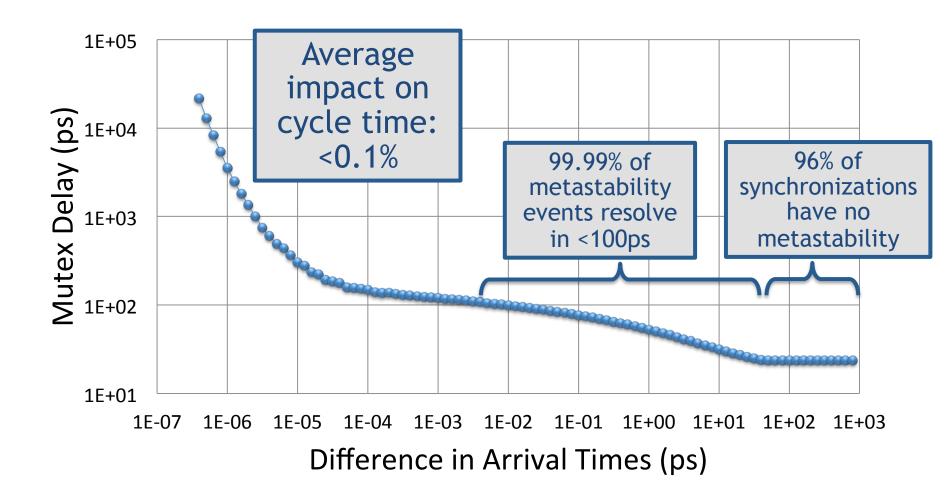

## Metastability in Pausible Clocks

## Clock Pauses Are Rare

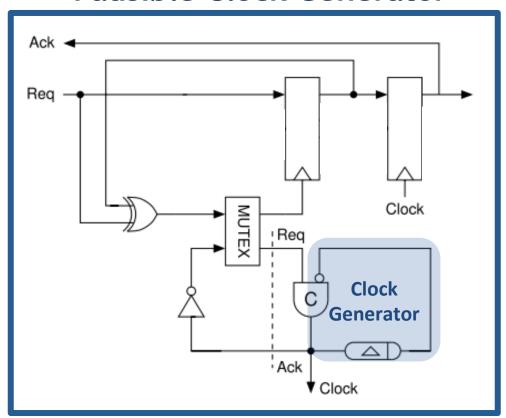

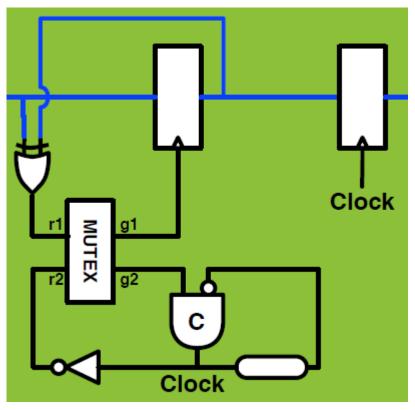

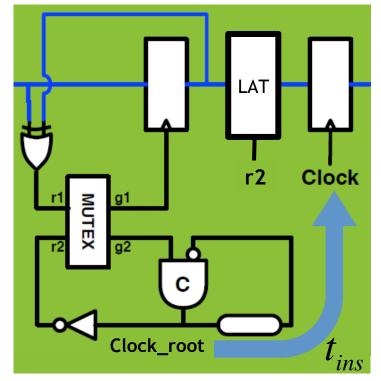

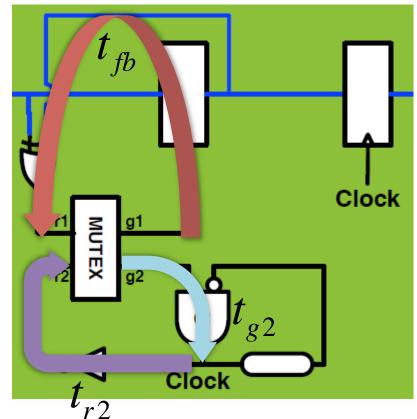

# Synchronization With Pausible Clock Generators

#### "Pausible Clock Generator"

Mutex and pausible clock safely synchronize the signal.

Synchronized signal arrives after (an average of) just 1 clock cycle!

"Demystifying Data Driven and Pausible Clocking Schemes," Mullins07

## Pausible Clocks: Our Contribution

- Prior work in pausible clocks:

- Proposed pausible clocking as a technique for lowlatency asynchronous interface crossings (Yun96)

- Integrated pausible clocks with asynchronous FIFOs to make GALS wrappers (Moore02, Fan09, others)

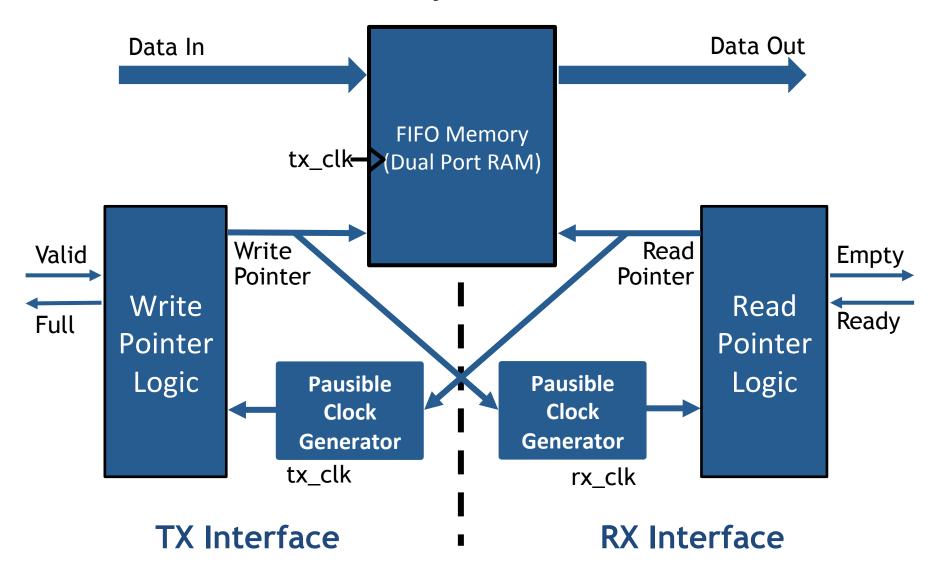

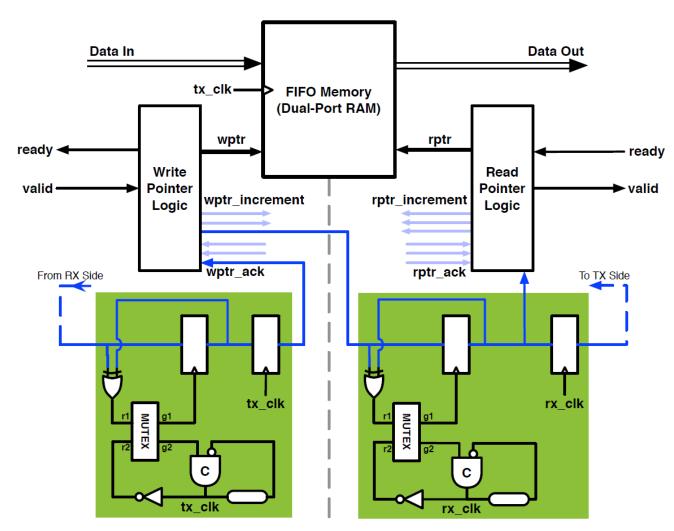

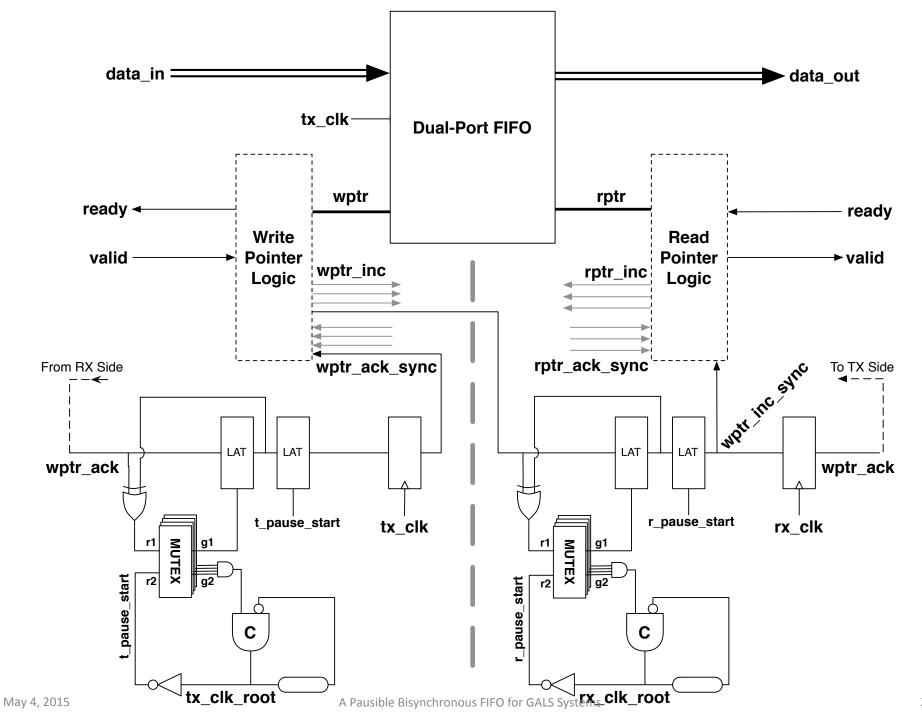

- We propose a circuit that:

- Pairs pausible clocking techniques with standard twoported synchronous FIFOs

- Uses a novel flow-control scheme that enables lowlatency asynchronous boundary crossings

- Integrates easily with standard toolflows

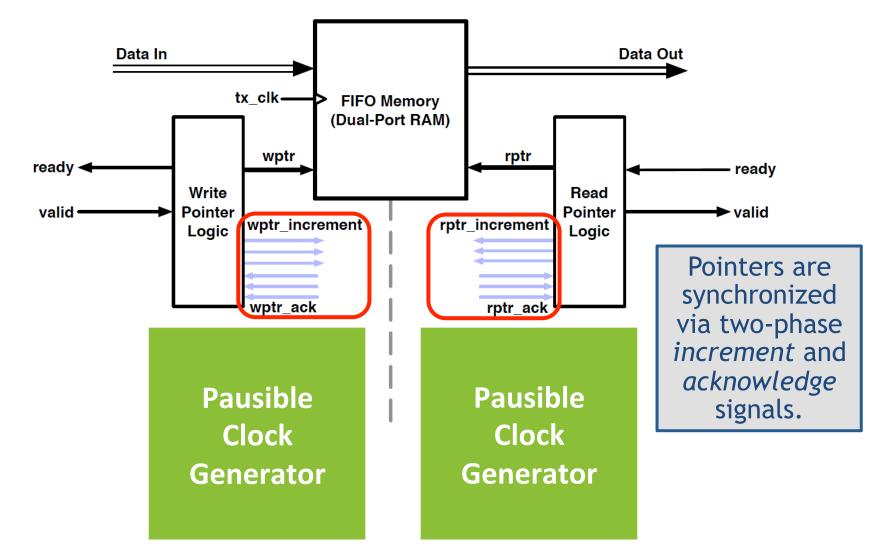

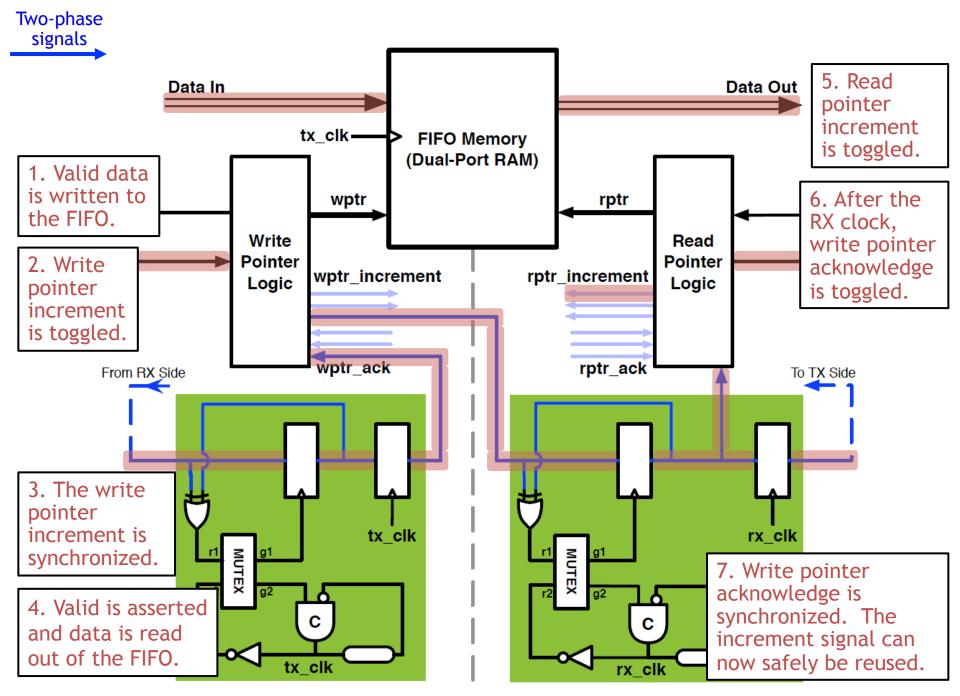

## A Pausible Bisynchronous FIFO

## A Pausible Bisynchronous FIFO

## A Pausible Bisynchronous FIFO

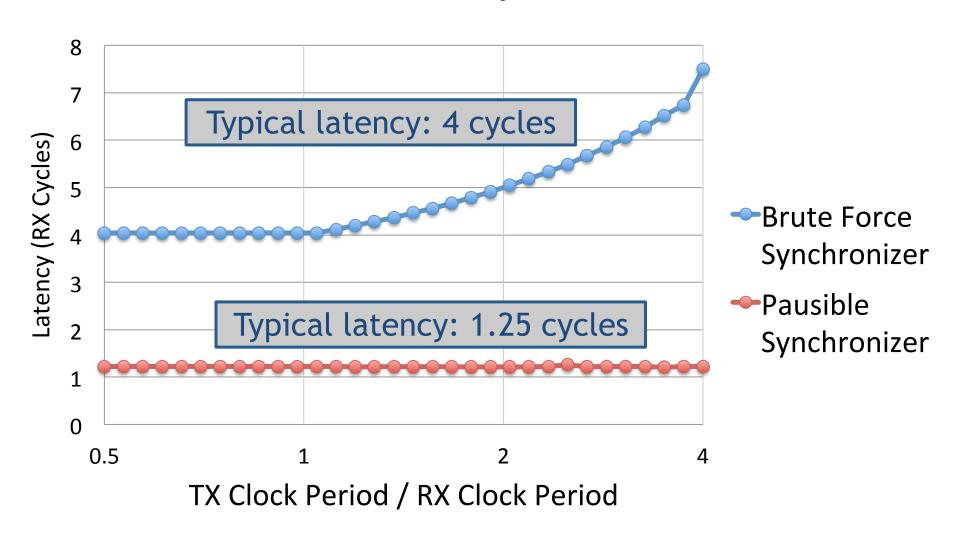

## Simulation Results: Brute Force Synchronizer

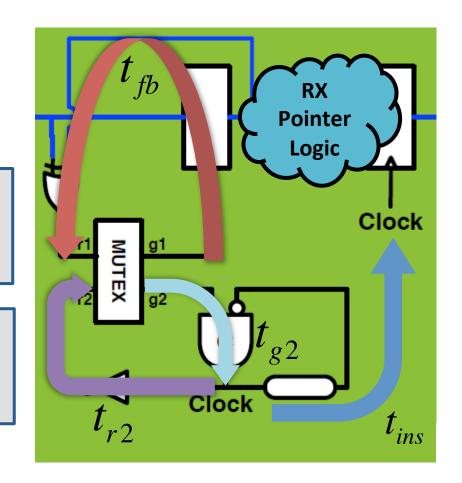

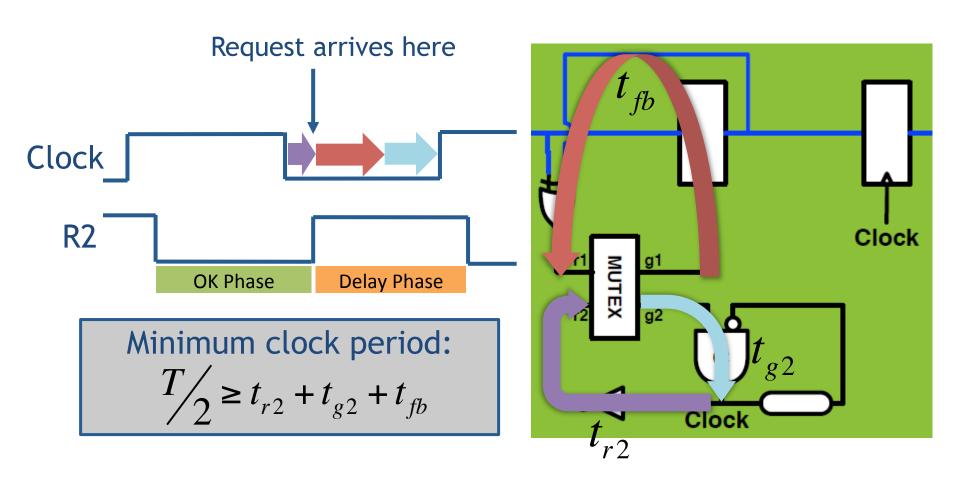

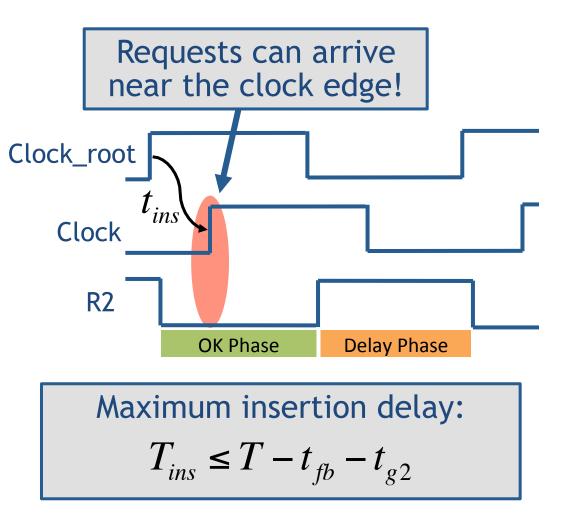

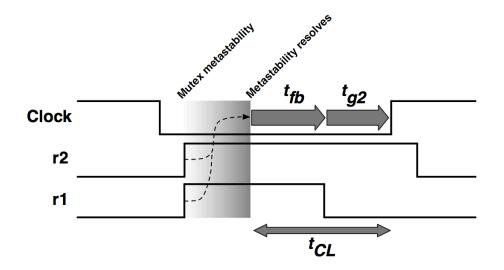

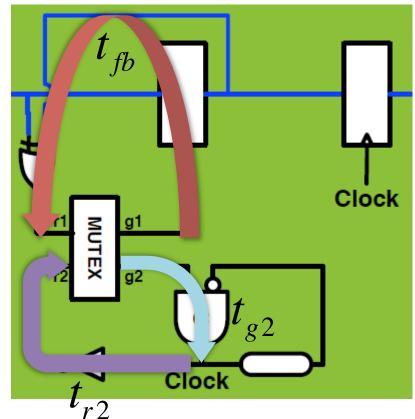

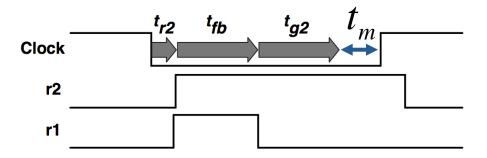

## Pausible Clocking Timing Constraints

### Minimum clock period:

$$T/2 \ge t_{r2} + t_{g2} + t_{fb}$$

#### Maximum insertion delay:

$$T_{ins} \le T - t_{fb} - t_{g2}$$

### Maximum same-cycle work:

$$T_{CL} \le t_{fb} + t_{g2} + T_{ins}$$

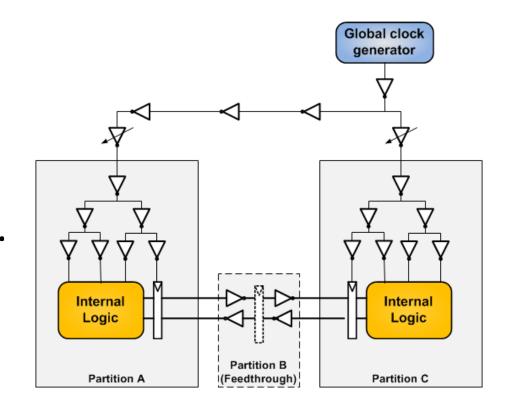

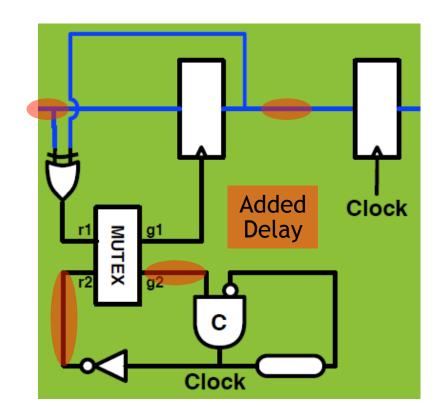

# Pausible Clocking Limitations: Where to Put the Mutexes?

# Pausible Clocking Limitations: Where to Put the Mutexes?

#### **Option 1: Mutexes at the interface**

Reduces maximum clock rate

#### **Option 2: Mutexes at the center**

- Increases latency

- + Improves maximum clock rate

- + Can bake the mutex into a black box with the clock generator

## Playing Nice with the Tools

- Most of the design is synchronous and works fine with synthesis tools

- FIFO is a standard dual- ported memory

- A single custom cell is needed

- Custom timing constraints at clock domain crossings

# Synchronizer Comparison

| Design                      | Average Latency (cycles) | Area (um²) | Power (mW) | Energy<br>(fJ/bit) |

|-----------------------------|--------------------------|------------|------------|--------------------|

| Synchronous<br>Interface    | 1                        | 4968       | 4.08       | 25.5               |

| Brute Force<br>Synchronizer | ~4                       | 5005       | 6.03       | 37.7               |

| Pausible<br>Synchronizer    | ~1.5                     | 4808       | 5.41       | 33.8               |

## Summary

- Pausible clocks have key advantages over standard synchronizers, including low latency and zero probability of failure

- We designed a pausible bisynchronous FIFO that pairs pausible clocking techniques with standard two-ported synchronous FIFOs

- Fast asynchronous interfaces that work well with standard toolflows are a key enabling technology of fine-grained GALS design

## References

- R. Mullins and S. Moore, "Demystifying Data-Driven and Pausible Clocking Schemes," in *Proc. IEEE Symposium on Asynchronous Cir- cuits and Systems*, 2007, pp. 175–185.

- K. Yun and R. Donohue, "Pausible clocking: a first step toward heterogeneous systems," in *Proc. IEEE International* Conference on Computer Design, 1996, pp. 118–123.

- S. Moore *et al.*, "Point to point GALS interconnect," in *Proc. IEEE Symposium on Asynchronous Circuits and Systems*, 2002, pp. 69–75.

- X. Fan et al., "Analysis and optimization of pausible clocking based GALS design," *IEEE International Conference Computer Design*, 2009.

## Questions?

# **Backup Slides**

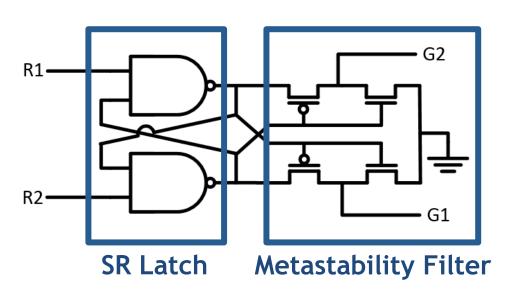

### **Mutex Circuit**

| R1 | <b>R2</b> | <b>G1</b>                                  | G2 |

|----|-----------|--------------------------------------------|----|

| 0  | 0         | 0                                          | 0  |

| 1  | 0         | 1                                          | 0  |

| 0  | 1         | 0                                          | 1  |

| 1  | 1         | R1 first -> G1 high<br>R2 first -> G2 high |    |

- Only G1 or G2 can be high at once (never both)

- If R1 and R2 transition high simultaneously, metastability can result

- The "metastability filter" keeps both outputs low until metastability resolves

## Simulation Setup

- Implemented interface in Verilog

- Allows direct comparison to brute-force synchronizers via drop-in replacement

## Minimum Clock Period

## **Insertion Delay**

# Combinational Logic Delay $T_{CL}$

Maximum same-cycle work:

$$T_{CL} \le t_{fb} + t_{g2} + T_{ins}$$

## Metastability Margin $t_m$

### Minimum clock period:

$$T/2 \ge t_{r2} + t_{g2} + t_{fb}$$

### Metastability margin:

$$t_m = \frac{T}{2} - (t_{r2} + t_{g2} + t_{fb})$$

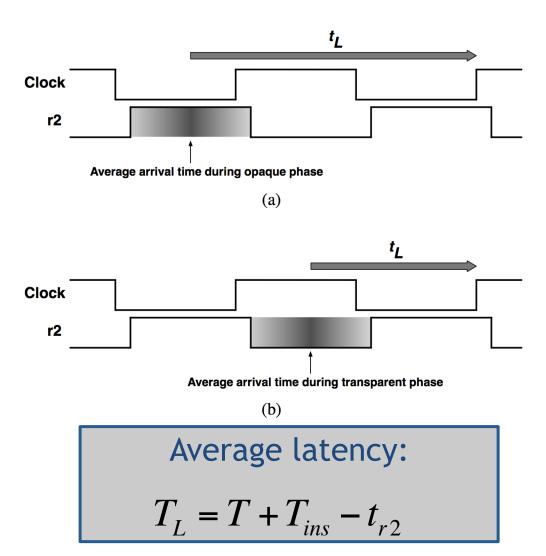

## **Average Latency**