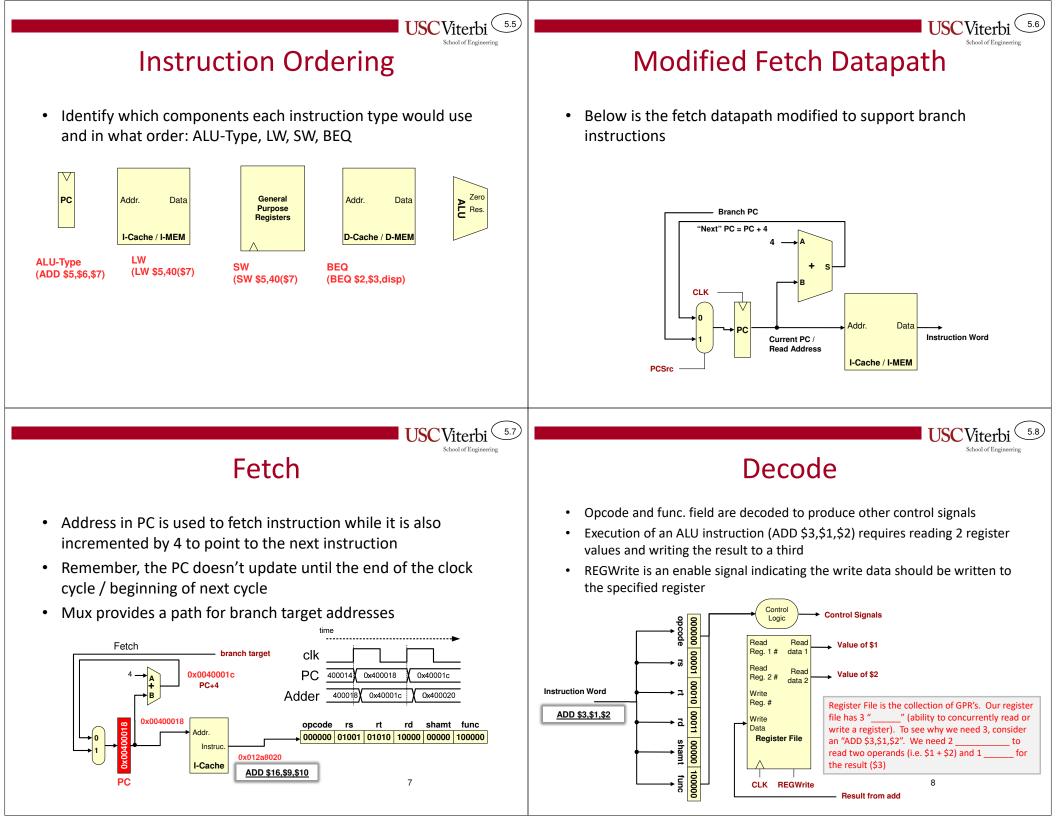

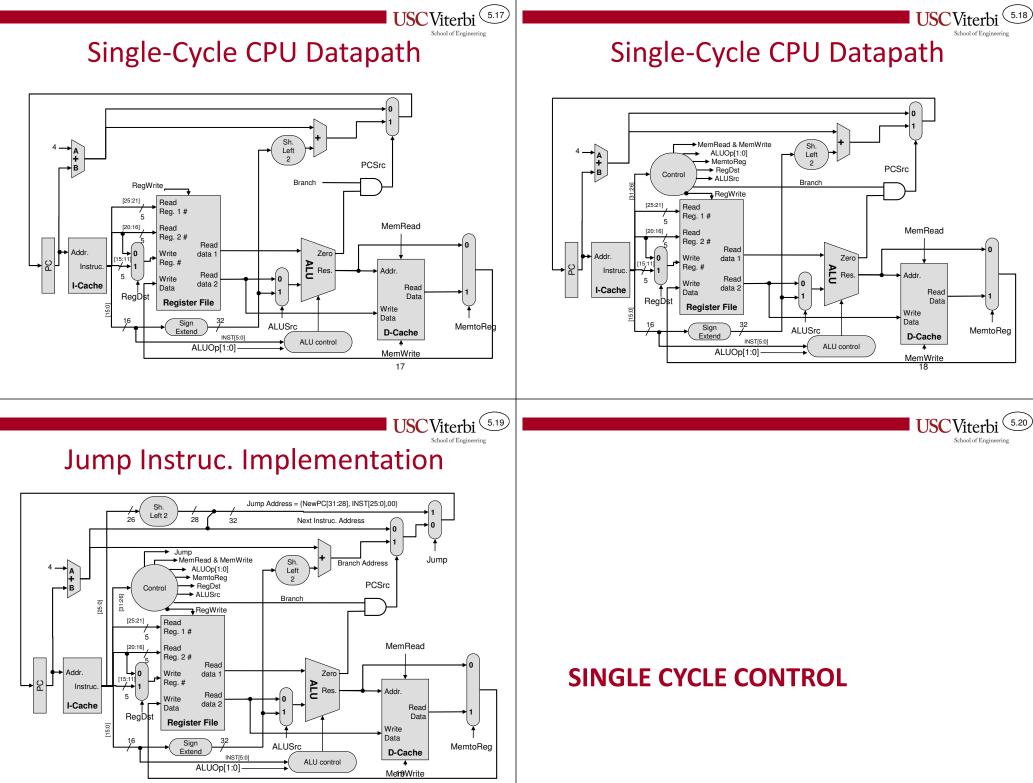

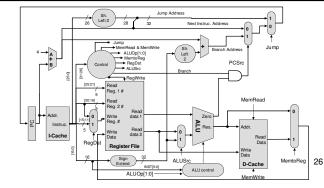

#### **CPU Organization Scope** We will build a CPU to implement our subset of the MIPS ISA - Memory Reference Instructions: Load Word (LW) FF 457 Unit 5 Store Word (SW) Arithmetic and Logic Instructions: • ADD, SUB, AND, OR, SLT Branch and Jump Instructions: Single Cycle CPU Branch if equal (BEQ) Jump unconditional (J) Datapath and Control These basic instructions exercise a majority of the necessary datapath and control logic for a more complete implementation 2 **USC**Viterbi Single-Cycle Datapath **CPU** Implementations To start, let us think about what operations need to be We will go through two implementations performed for the basic instructions Single-cycle CPU (CPI = 1) • All instructions go through the following steps: • All instructions execute in a single, long clock cycle - Fetch: Use to fetch instruction Multi-cycle CPU (CPI = n) - Decode & Register/Operand Fetch: Determine instruction type and Instructions can take a different number of short clock cycles to execute fetch any register operands needed Recall that a program execution time is: Once decoded, different instructions require different (Instruction count) x (CPI) x (Clock cycle time) operations In single-cycle implementation cycle time must be set for longest - ALU instructions: Perform Add, Sub, etc. and write result back to instruction thus requiring shorter instructions to wait register Multi-cycle implementation breaks logic into sub-operations each taking one short clock cycle; then each instruction takes only the LW / SW: Calculate address ( ) and perform memory access

- Ew 7 5W. Calculate address (\_\_\_\_\_) and perform memory ac

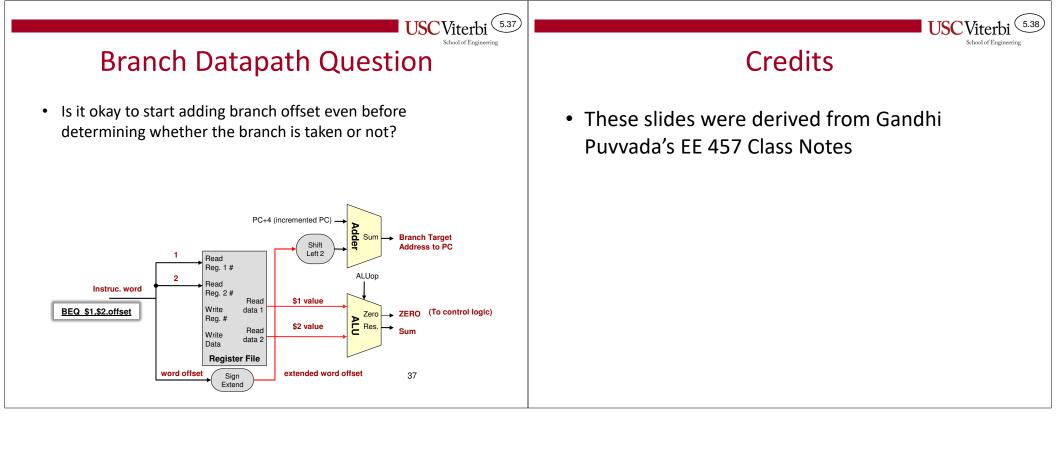

- BEQ / J: Update PC (possible based on \_\_\_\_\_)

- Let us start with fetching an instruction and work our way through the necessary components

number of clocks (i.e. CPI) it needs

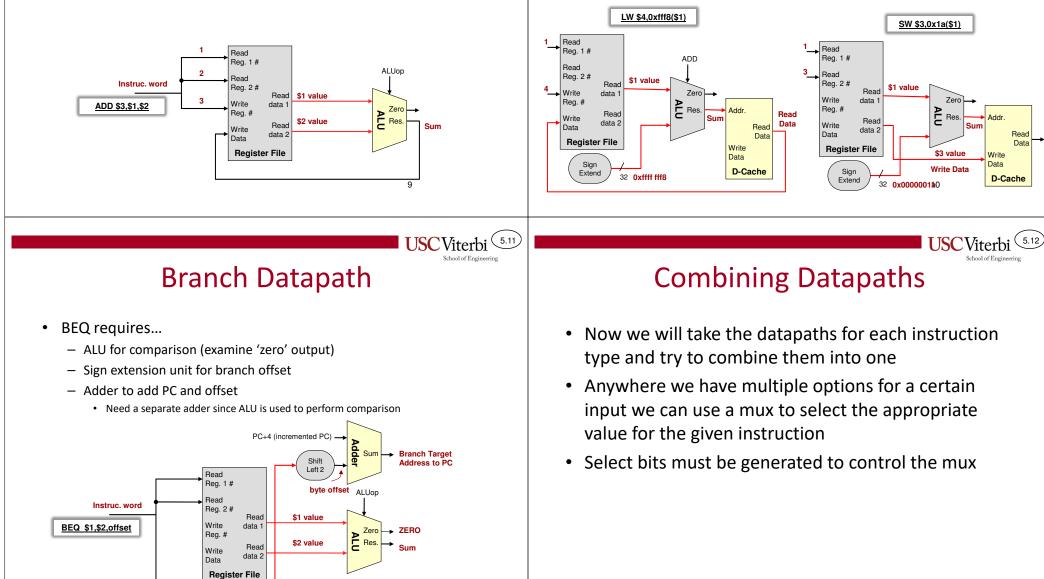

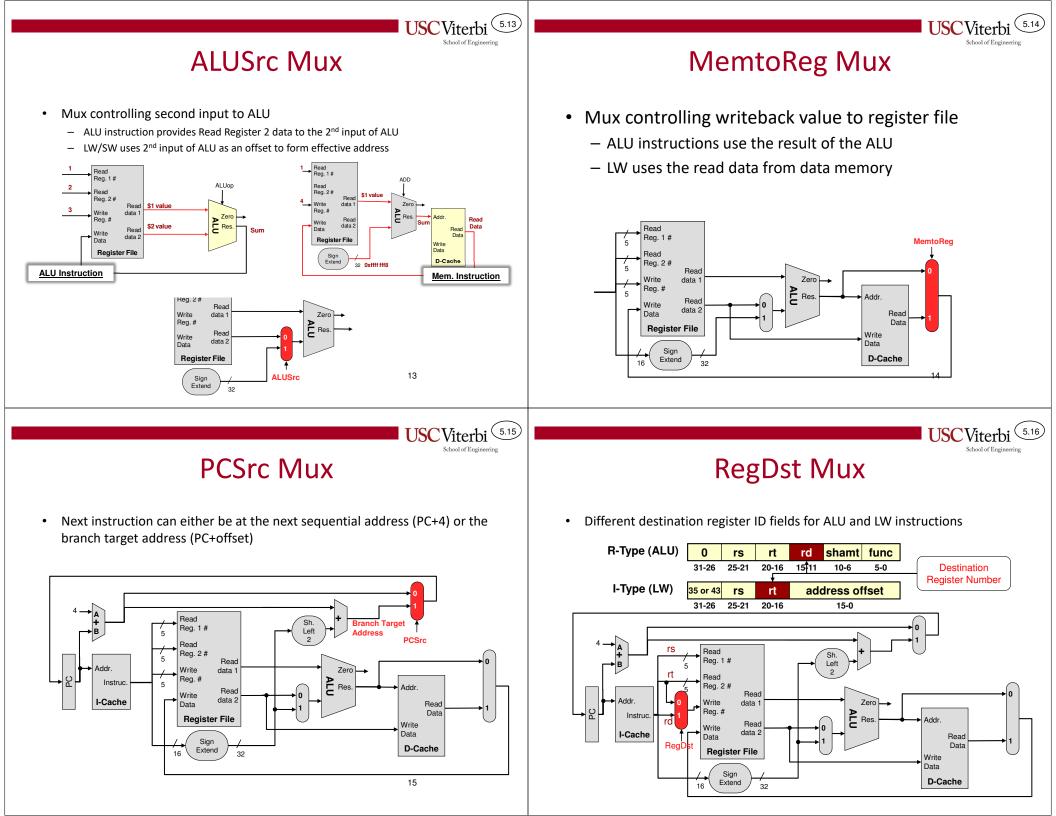

# Datapath for ALU instruction

- ALU takes inputs from register file and performs the add, sub, and, or, slt, operations

- Result is written back to dest. register

word offset

Sign

extended word offset

11

#### **Memory Access Datapath**

- Operands are read from register file while offset is sign extended

- ALU calculates \_\_\_\_

- Memory access is performed

- If LW, \_\_\_\_\_

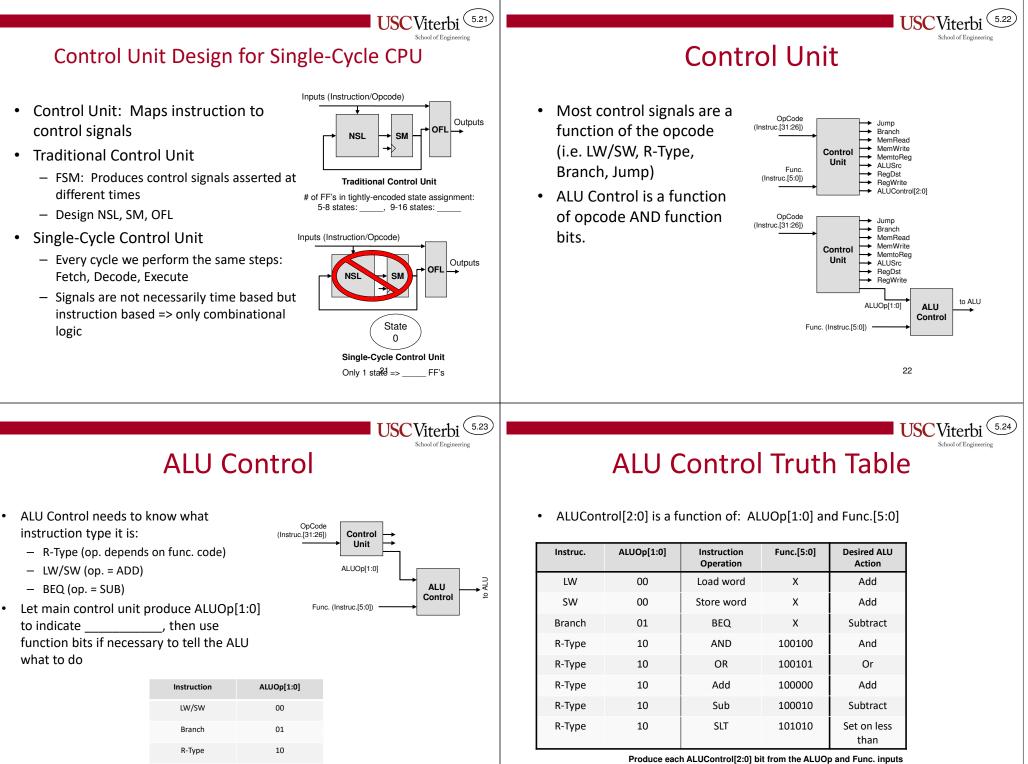

Control unit maps instruction opcode to ALUOp[1:0] encoding

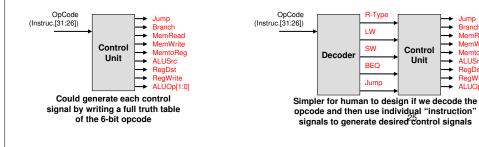

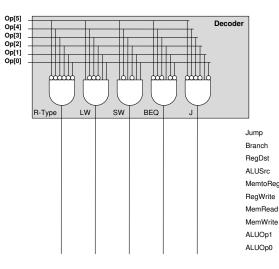

### **Control Signal Generation**

- Other control signals are a function of the opcode

- We could write a full truth table or (because we are only • implementing a small subset of instructions) simply decode the opcodes of the specific instructions we are implementing and use those intermediate signals to generate the actual control signals

USC Viterbi (5.27) School of Engineering

Branch

-

Control

Unit

MemBe

MemWrite

MemtoRec

ALUOp[1:0]

-> ALUSrc

ReaDst

RegWrite

USC Viterbi (5.25)

### **Control Signal Logic**

## **Control Signal Truth Table**

| R-<br>Type | LW | SW | BEQ | J | Jump | Branch | Reg<br>Dst | ALU<br>Src | Memto-<br>Reg | Reg<br>Write | Mem<br>Read | Mem<br>Write | ALU<br>Op[1] | ALU<br>Op[0] |

|------------|----|----|-----|---|------|--------|------------|------------|---------------|--------------|-------------|--------------|--------------|--------------|

| 1          | 0  | 0  | 0   | 0 | 0    | 0      |            |            |               |              | 0           | 0            | 1            | 0            |

| 0          | 1  | 0  | 0   | 0 | 0    | 0      |            |            |               |              | 1           | 0            | 0            | 0            |

| 0          | 0  | 1  | 0   | 0 | 0    | 0      |            |            |               |              | 0           | 1            | 0            | 0            |

| 0          | 0  | 0  | 1   | 0 | 0    | 1      |            |            |               |              | 0           | 0            | 0            | 1            |

| 0          | 0  | 0  | 0   | 1 | 1    | Х      |            |            |               |              | 0           | 0            | Х            | Х            |

5.28 **USC**Viterbi School of Engineering

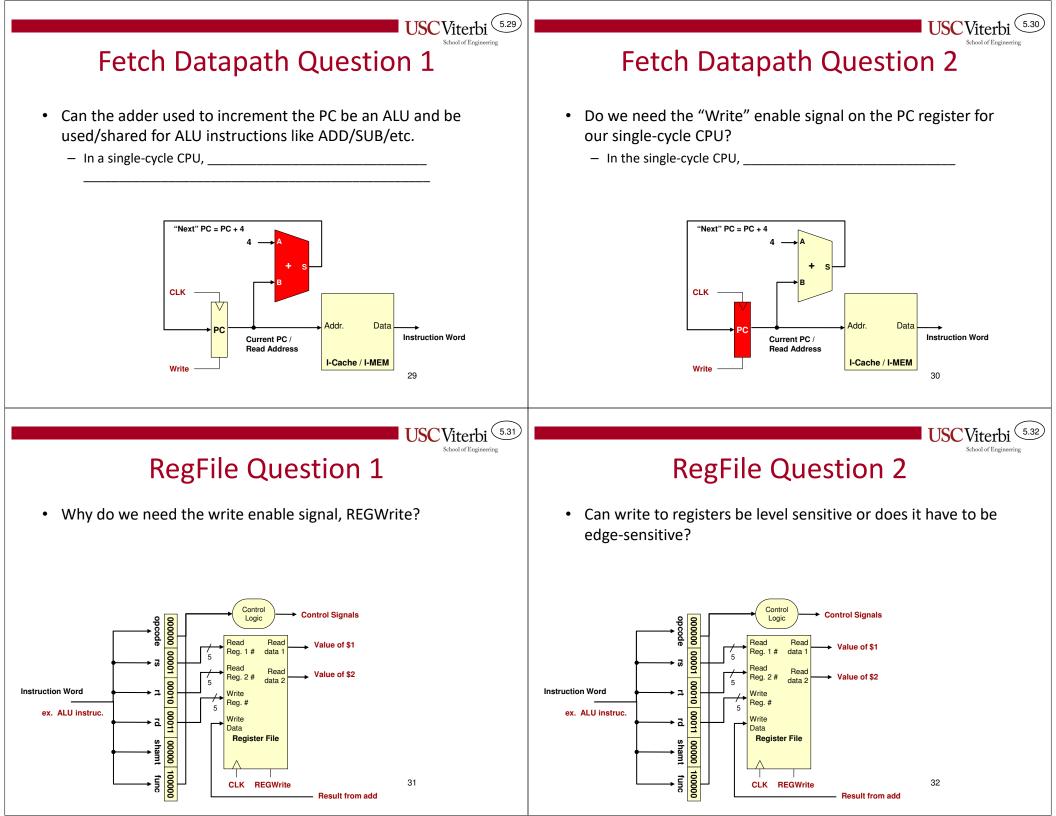

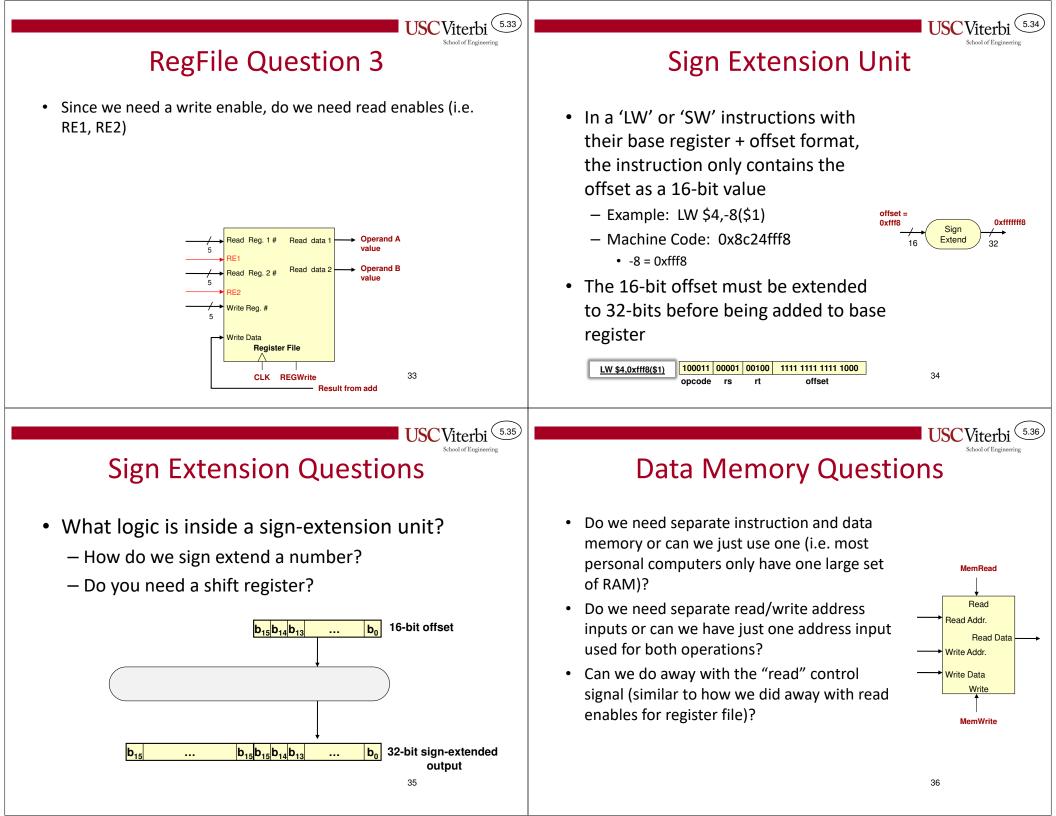

### **DATAPATH QUESTIONS**

27