# EE 457 Unit 3

Instruction Sets

With Focus on our Case Study: MIPS

### **INSTRUCTION SET OVERVIEW**

## **Instruction Sets**

- Defines the software interface of the processor and memory system

- Instruction set is the vocabulary the HW can understand and the SW is composed with

- Most assembly/machine instructions fall into one of three categories

#### Instruction Set Architecture (ISA)

**USC**Viterbi

• 2 approaches

3.3

**USC**Viterbi

- CISC = Complex instruction set computer

- Large, rich vocabulary

- More work per instruction, slower clock cycle

- RISC = Reduced instruction set computer

- Small, basic, but *sufficient* vocabulary

- Less work per instruction, faster clock cycle

- Usually a simple and small set of instructions with regular format facilitates building faster processors

# **MIPS ISA**

- RISC Style

- 32-bit internal / 32-bit external data size

- Registers and ALU are 32-bits wide

- Memory bus is logically 32-bits wide (though may be physically wider)

- Registers

- 32 General Purpose Registers (GPR's)

- For integer and address values

- A few are used for specific tasks/values

- 32 Floating point registers

- Fixed size instructions

- All instructions encoded as a single 32-bit word

- Three operand instruction format (dest, src1, src2)

- Load/store architecture (all data operands must be in registers and thus loaded from and stored to memory explicitly)

#### **MIPS Programmer-Visible Registers**

- General Purpose Registers (GPR's)

Hold data operands or addresses

- (pointers) to data stored in memory Special Purpose Registers

- special Purpose Registe

- PC: \_\_\_\_\_\_(32-bits)

Holds the \_\_\_\_\_\_of the next

\_\_\_\_\_\_to be fetched from

memory & executed

- HI: Hi-Half Reg. (32-bits)

- For MUL, holds 32 MSB's of result. For DIV, holds 32-bit remainder

- LO: Lo-Half Reg. (32-bits)

For MUL, holds 32 LSB's of result. For DIV, holds 32-bit

quotient

| GPR's        |           |                     |

|--------------|-----------|---------------------|

| \$0 - \$31   | MIPS Core |                     |

|              |           |                     |

|              |           |                     |

| ₹<br>32-bits |           |                     |

| PC:          |           |                     |

|              |           | МЕМ                 |

| HI:          |           | 0xA140 add          |

| LO:          |           | ?? <mark>sub</mark> |

|              |           |                     |

Special Purpose Registers

JSC Viterbi 3.8

#### USC Viterbi (3.7)

School of Engineering

#### **MIPS Programmer-Visible Registers**

- Coprocessor 0 Registers

- Status Register

- Holds various control bits for processor modes, handling interrupts, etc.

- Cause Register

- Holds information about exception (error) conditions

- Coprocessor 1 Registers

- Floating-point registers

- Can be used for single or double-precision (i.e. at least 64-bits wides)

GPR's

\$0 - \$31

\$f0 - \$f31

32-bits

64 or more

Coprocessor 1

Floating-point Regs.

Status:

LO:

Coprocessor 0

Status & Control Regs

MIPS Core

# **MIPS GPR's**

| Assembler Name | Reg. Number | Description                                       |

|----------------|-------------|---------------------------------------------------|

| \$zero         | \$0         | Constant 0 value                                  |

| \$at           | \$1         | Assembler temporary                               |

| \$v0-\$v1      | \$2-\$3     | Procedure return values or expression evaluation  |

| \$a0-\$a3      | \$4-\$7     | Arguments/parameters                              |

| \$t0-\$t7      | \$8-\$15    | Temporaries                                       |

| \$s0-\$s7      | \$16-\$23   | Saved Temporaries                                 |

| \$t8-\$t9      | \$24-\$25   | Temporaries                                       |

| \$k0-\$k1      | \$26-\$27   | Reserved for OS kernel                            |

| \$gp           | \$28        | Global Pointer (Global and static variables/data) |

| \$sp           | \$29        | Stack Pointer                                     |

| \$fp           | \$30        | Frame Pointer                                     |

| \$ra           | \$31        | Return address for current procedure              |

Special Purpose Registers

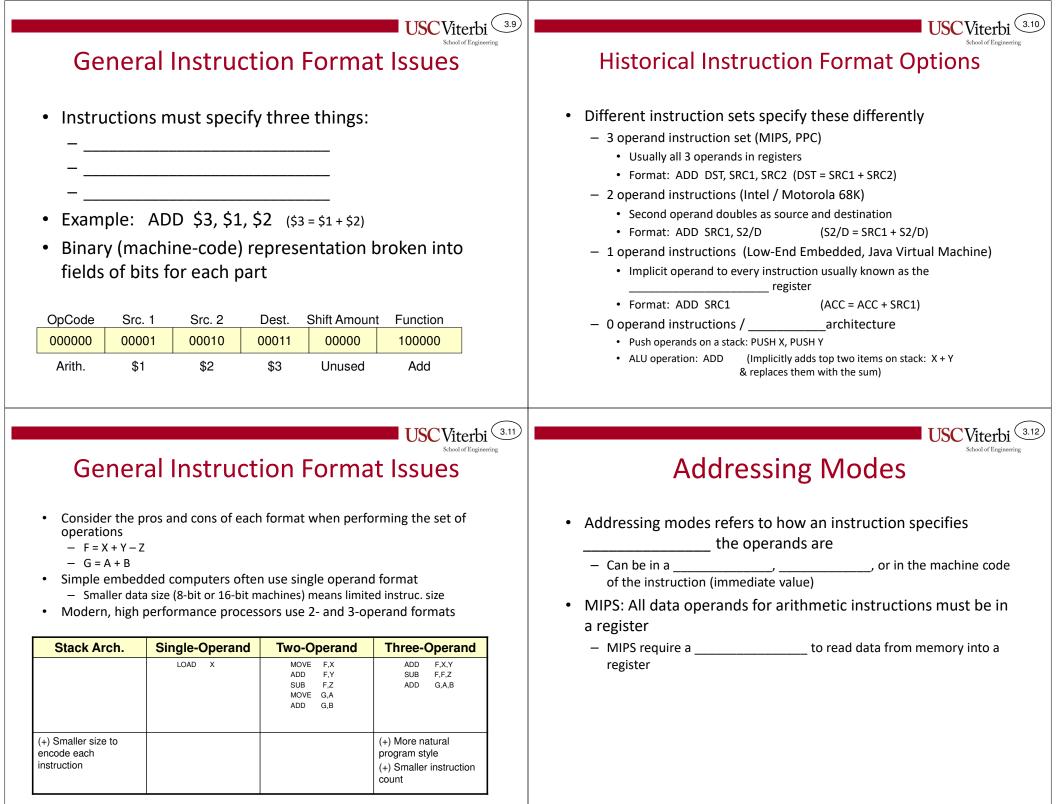

#### **MIPS Instruction Format**

- CISC and other older architectures use a variable size instruction to match the varying operand specifications (memory addresses, etc.)

- 1 to 8 bytes

- MIPS uses a FIXED-length instruction as do most RISC-style instruction sets

- Every instruction is 32-bits (4-bytes)

- One format (field breakdown) is not possible to support all the different instructions

- MIPS supports 3 instruction formats: R-Type, I-Type, J-Type

USC Viterbi (3.19)

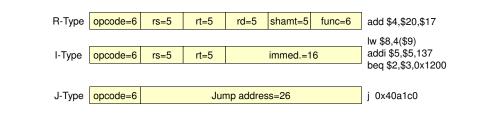

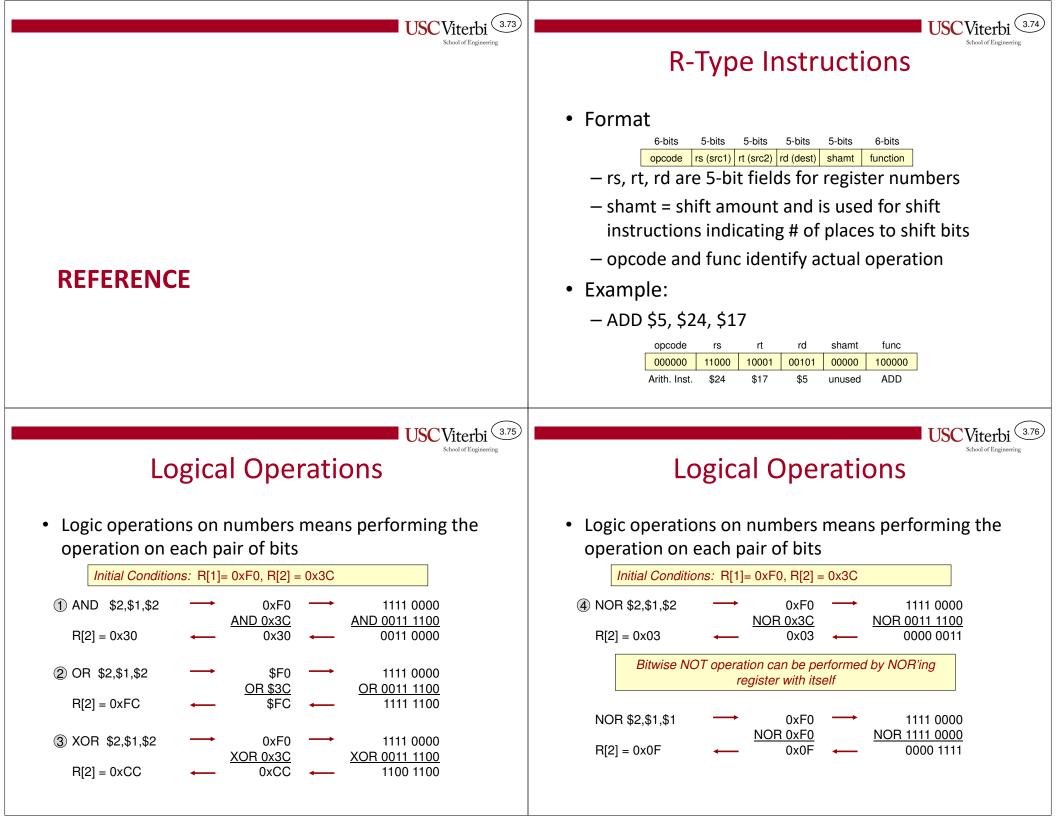

# **R-Type Instructions**

Format

6-bits

5-bits

5-bits

5-bits

6-bits

opcode

rs (src1)

rt (src2)

rd (dest)

shamt

function

- rs, rt, rd are 5-bit fields for register numbers

- shamt = shift amount and is used for shift instructions indicating # of places to shift bits

- opcode and func identify actual operation

- Example:

- ADD \$5, \$24, \$17

| opcode       | rs    | rt    | rd    | shamt  | func   |

|--------------|-------|-------|-------|--------|--------|

| 000000       | 11000 | 10001 | 00101 | 00000  | 100000 |

| Arith. Inst. | \$24  | \$17  | \$5   | unused | ADD    |

ALU (R-Type) Instructions

Memory Access, Branch, & Immediate (I-Type) Instructions

### **MIPS INSTRUCTIONS**

#### USC Viterbi (3.20

#### R-Type Arithmetic/Logic Instructions

| C operator    | Assembly                             | Notes                                                                                                         |

|---------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------|

| +             | ADD Rd, Rs, Rt                       |                                                                                                               |

| -             | SUB Rd, Rs, Rt                       | Order: R[s] – R[t]. SUBU for unsigned                                                                         |

| *             | MULT Rs, Rt<br>MULTU Rs, Rt          | Result in HI/LO. Use mfhi and mflo instruction to move results                                                |

| *             | MUL Rd, Rs, Rt                       | If multiply won't overflow 32-bit result                                                                      |

| /             | DIV Rs, Rt<br>DIVU Rs, Rt            | R[s] / R[t].<br>Remainder in HI, quotient in LO                                                               |

| &             | AND Rd, Rs, Rt                       |                                                                                                               |

|               | OR Rd, Rs, Rt                        |                                                                                                               |

| ٨             | XOR Rd, Rs, Rt                       |                                                                                                               |

| ~( )          | NOR Rd, Rs, Rt                       | Can be used for bitwise-NOT (~)                                                                               |

| <<            | SLL Rd, Rs, shamt<br>SLLV Rd, Rs, Rt | Shifts R[s] left by shamt (shift amount) or R[t] bits                                                         |

| >> (signed)   | SRA Rd, Rs, shamt<br>SRAV Rd, Rs, Rt | Shifts R[s] right by shamt or R[t] bits replicating sign bit to maintain sign                                 |

| >> (unsigned) | SRL Rd, Rs, shamt<br>SRLV Rd, Rs, Rt | Shifts R[s] left by shamt or R[t] bits shifting in 0's                                                        |

| <, >, <=, >=  | SLT Rd, Rs, Rt<br>SLTU Rd, Rs, Rt    | $\label{eq:intermediate} \begin{split} IF(R[s] < R[t]) \; THEN \; R[d] &= 1 \\ ELSE \; R[d] &= 0 \end{split}$ |

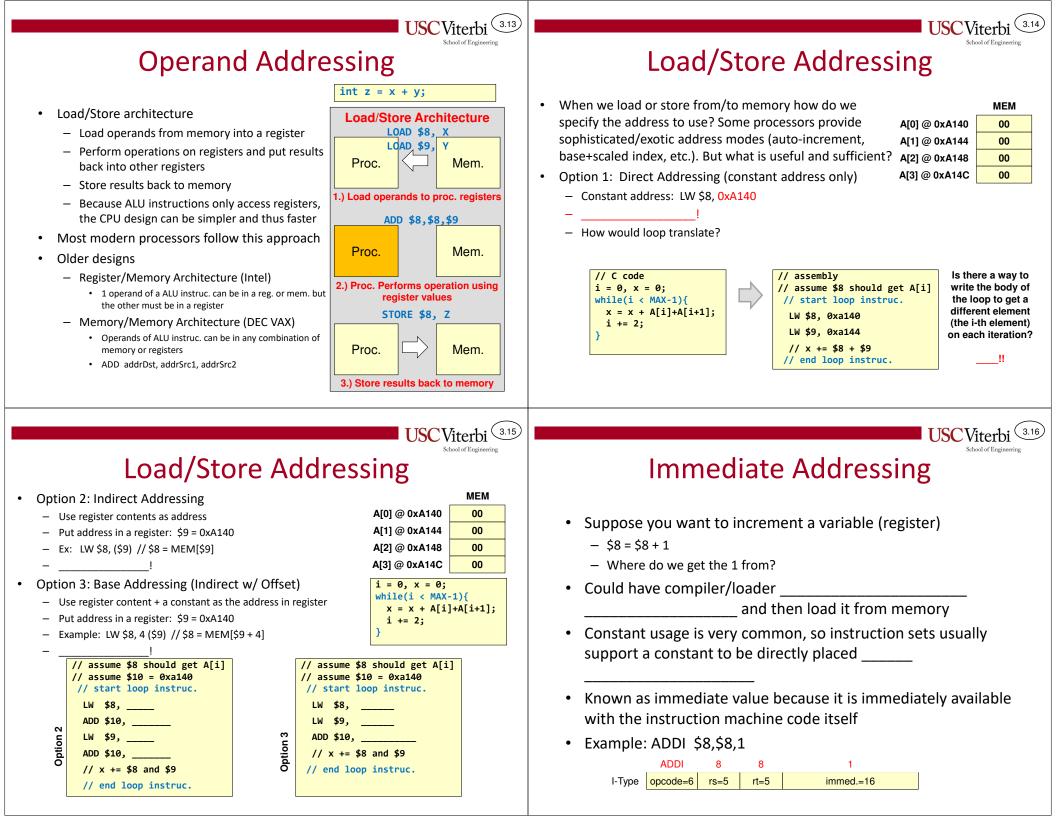

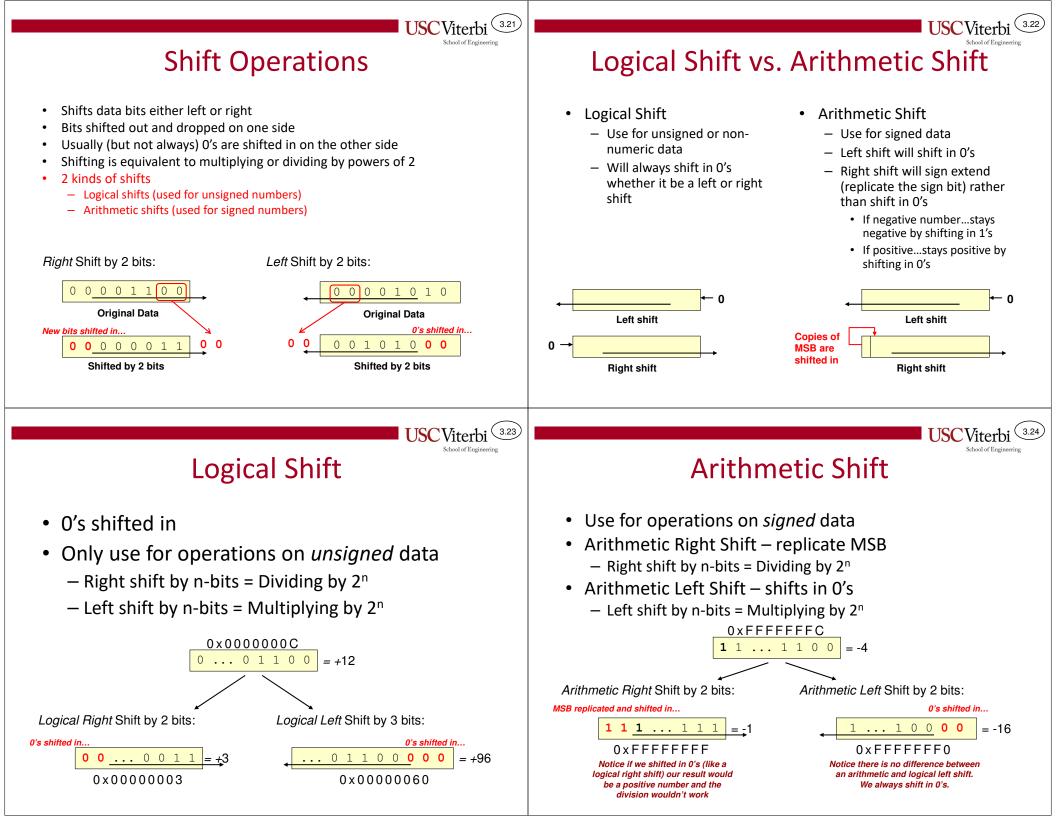

# **Logical Shift Instructions**

- SRL instruction Shift Right Logical

- SLL instruction Shift Left Logical

- Format:

- SxL rd, rt, shamt

- SxLV rd, rt, rs

- Notes:

- shamt limited to a 5-bit value (0-31)

- SxLV shifts data in rt by number of places specified in rs

- Examples

- SRL \$5, \$12, 7

- SLLV \$5, \$12, \$20

| opcode       | rs     | rt    | rd    | shamt  | func   |

|--------------|--------|-------|-------|--------|--------|

| 000000       | 00000  | 10001 | 00101 | 00111  | 000010 |

| Arith. Inst. | unused | \$12  | \$5   | 7      | SRL    |

| 000000       | 10100  | 10001 | 00101 | 00000  | 000100 |

| Arith. Inst. | \$20   | \$12  | \$5   | unused | SLLV   |

# **I-Type Instructions**

Format

| 6-bits | 5-bits    | 5-bits       | 16-bits   |

|--------|-----------|--------------|-----------|

| opcode | rs (src1) | rt (src/dst) | immediate |

- rs, rt are 5-bit fields for register numbers

- immediate is a 16-bit constant

- opcode identifies actual operation

- Example:

- ADDI \$5, \$24, 1

- \$5, -8(\$3) – LW

| opcode | rs    | rt    | immediate           |

|--------|-------|-------|---------------------|

| 001000 | 11000 | 00101 | 0000 0000 0000 0001 |

| ADDI   | \$24  | \$5   | 20                  |

| 010111 | 00011 | 00101 | 1111 1111 1111 1000 |

| LW     | \$3   | \$5   | -8                  |

|        |       |       |                     |

## **Arithmetic Shift Instructions**

- SRA instruction Shift Right Arithmetic

- Use SLL for arithmetic left shift

- Format:

- SRA rd, rt, shamt

- SRAV rd, rt, rs

- Notes:

- shamt limited to a 5-bit value (0-31)

- SRAV shifts data in rt by number of places specified in rs

- Examples

- SRA \$5, \$12, 7

- SRAV \$5, \$12, \$20

| opcode       | rs     | rt    | rd    | shamt  | func   |

|--------------|--------|-------|-------|--------|--------|

| 000000       | 00000  | 10001 | 00101 | 00111  | 000011 |

| Arith. Inst. | unused | \$12  | \$5   | 7      | SRA    |

| 000000       | 10100  | 10001 | 00101 | 00000  | 000111 |

| Arith. Inst. | \$20   | \$12  | \$5   | unused | SRAV   |

USC Viterbi (3.27)

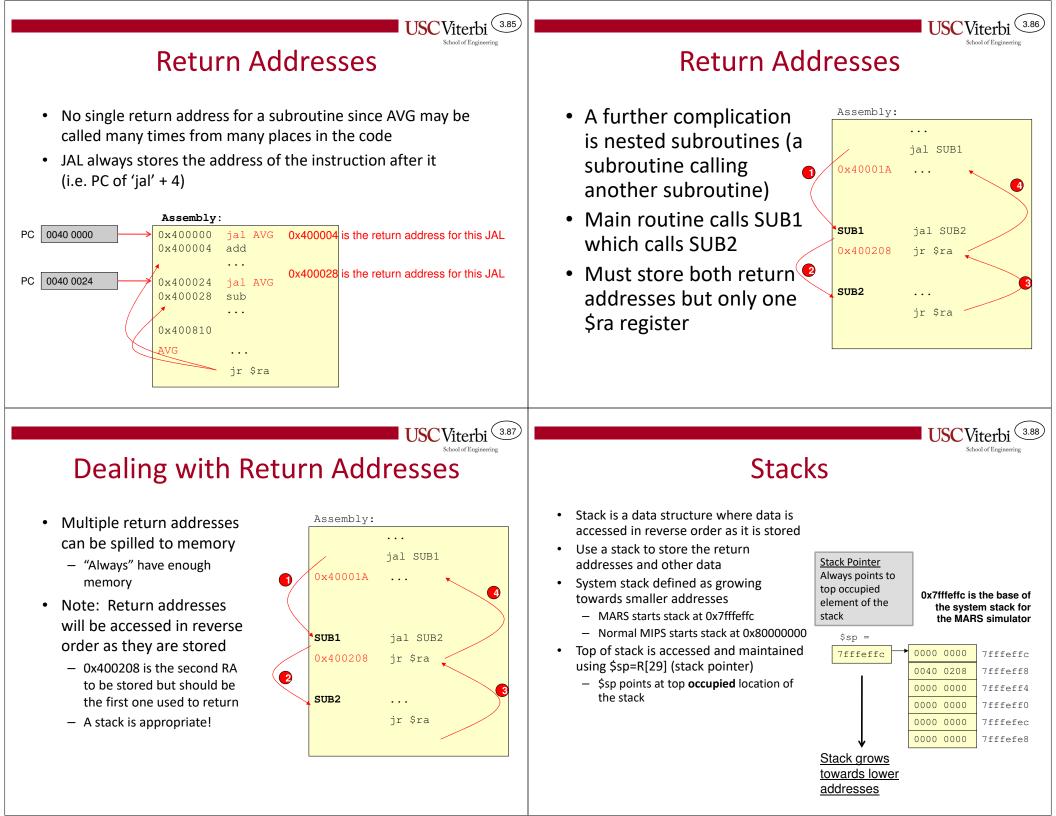

# Immediate Operands

USC

- Most ALU instructions also have an immediate form to be used when one operand is a constant value

- Syntax: ADDI Rs, Rt, imm

- Because immediates are limited to 16-bits, they must be extended to a full 32bits when used the by the processor

- Arithmetic instructions always \_\_\_\_\_\_ to a full 32-bits even for unsigned instructions (addiu)

- Logical instructions always \_\_\_\_\_\_ to a full 32-bits

- Examples:

- // R[4] = R[5] + \_\_\_\_\_ – ADDI \$4, \$5, -1 \$10, \$14, -4 - ORI // R[10] = R[14] |

| ,.,        |         |                                   |

|------------|---------|-----------------------------------|

| Arithmetic | Logical |                                   |

| ADDI       | ANDI    | Note: is unnecessary              |

| ADDIU      | ORI     | since we can use ADDI with        |

| SLTI       | XORI    | a <u>negative</u> immediate value |

| SLTIU      |         |                                   |

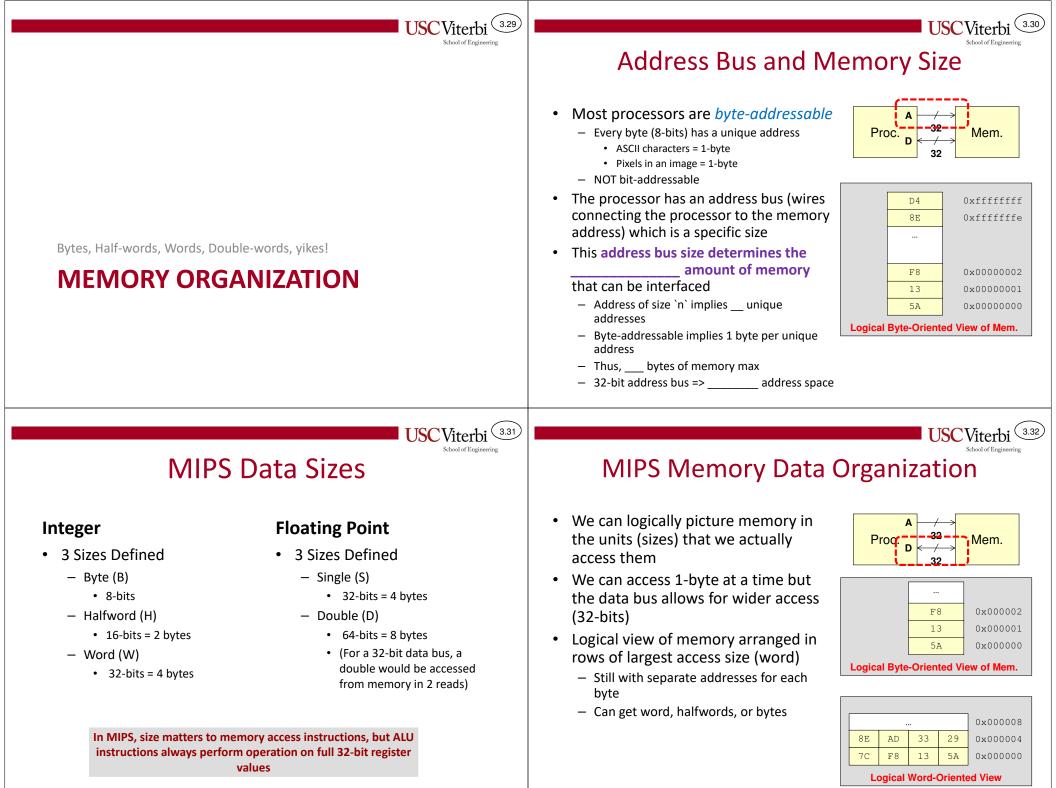

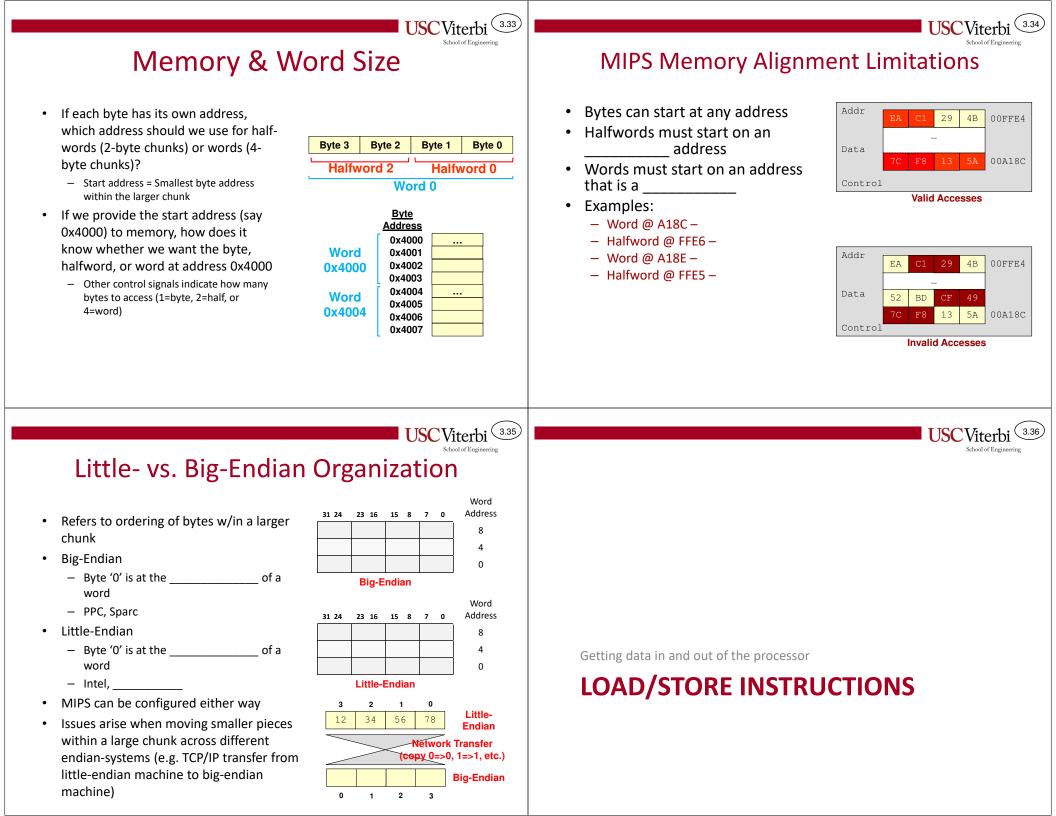

# Memory & Data Size

- Little-endian memory can be thought of as right justified

- Always provide the \_\_\_\_\_ of the desired data

- Size is explicitly defined by the instruction used

- Memory Access Rules

- Halfword or Word access must start on an address that is a multiple of that data size (i.e. half = multiple of 2, word = multiple of 4)

GPR

If address = 0x02

Sign Extend

Reg. =

31

7

0

**Bvte**

# Memory Read Instructions (Signed)

LB (Load Byte)

Provide address of desired byte Memory

7C

13 F8

5A

000004

000000

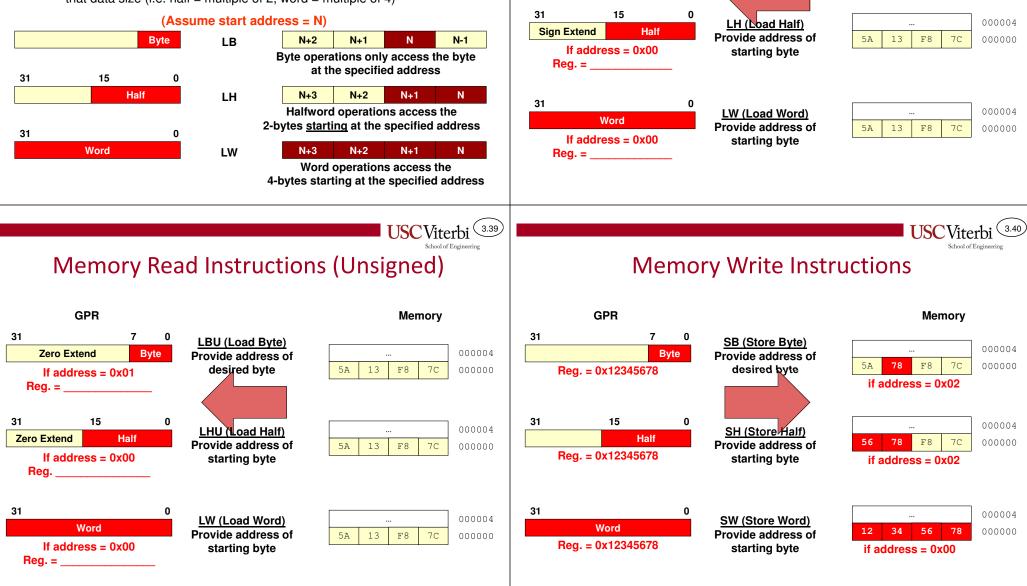

| USC Viterbi 3.41                                                                                                                                                                                                                                                                                                                   | USC Viterbi 3.42                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Load Format (LW,LH,LB)                                                                                                                                                                                                                                                                                                             | School of Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <ul> <li>LW Rt, offset(Rs)         <ul> <li>Rt = Destination register</li> <li>offset(Rs) = Address of desired data</li> <li>RTL: R[t] = M[ offset + R[s] ]</li> <li>offset limited to 16-bit signed number</li> </ul> </li> <li>Examples         <ul> <li>LW \$2, 0x40(\$3) // R[2] =</li></ul></li></ul>                         | <ul> <li>Examples <ul> <li>LB \$2,0x45(\$3) // R[2] =</li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                         |

| R[2]old val.F8BE97CD0x002048R[3]00002000134982FE0x002044R[4]0000204C5A12C5B70x002040                                                                                                                                                                                                                                               | R[2]old val.F8BE97CD0x002048R[3]00002000134982FE0x002044R[4]0000204C5A12C5B70x002040                                                                                                                                                                                                                                                                                                                                                                                              |

| USC Viterbi (3.43)                                                                                                                                                                                                                                                                                                                 | USC Viterbi (3.44)                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Store Format (SW,SH,SB)                                                                                                                                                                                                                                                                                                            | Loading an Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ul> <li>SW Rt, offset(Rs) <ul> <li>Rt = Source register</li> <li>offset(Rs) = Address to store data</li> <li>RTL: M[ offset + R[s] ] = R[t]</li> <li>offset limited to 16-bit signed number</li> </ul> </li> <li>Examples <ul> <li>SW \$2, 0x40(\$3)</li> <li>SB \$2, -5(\$4)</li> <li>SH \$2, 0xFFFE(\$4)</li> </ul> </li> </ul> | <ul> <li>If immediate (constant) 16-bits or less <ul> <li>Use ORI or ADDI instruction with \$0 register</li> <li>Examples <ul> <li>ADDI \$2, \$0, -1 // R[2] = 0 - 1 = -1</li> <li>ORI \$2, \$0, 0xF110 // R[2] = 0   0xF110 = 0xF110</li> </ul> </li> <li>If immediate more than 16-bits <ul> <li>Immediates limited to 16-bits so we must load constant with a 2 instruction sequence using the special LUI (Load Upper Immediate) instruction</li> </ul> </li> </ul></li></ul> |

| R[2]123489AB89AB97CD0x002048R[3]00002000AB4982FE0x002044R[4]0000204C123489AB0x002040                                                                                                                                                                                                                                               | - To load \$2 with 0x12345678                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

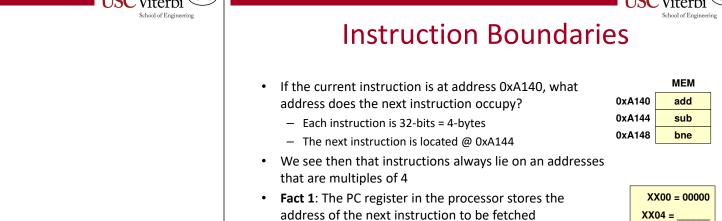

- Fact 2: Registers are needed when we want to store *variable* bits

- Fact 3: Addresses are 32-bits in MIPS

- Do we need a 32-bit register for the PC?

XX08 = \_\_\_\_\_ XX0c = \_\_\_\_\_ XX10 = \_\_\_\_\_ Multiples

Multiples of 4 in hex and binary

USC Viterbi (3.47)

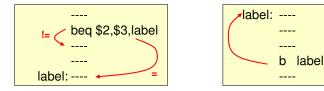

#### **Branch Instructions**

• Conditional Branches

**Program Flow Control**

- Branches only if a particular condition is true

**BRANCH INSTRUCTIONS**

- Fundamental Instrucs.: BEQ (if equal), BNE (not equal)

- Syntax: BNE/BEQ Rs, Rt, label

- Compares Rs, Rt and if EQ/NE, branch to label, else continue

- Unconditional Branches

- Always branches to a new location in the code

- Instruction: \_\_\_\_\_

- Pseudo-instruction: B label

**Two-Operand Compare & Branches**

- Two-operand comparison is accomplished using the SLT/SLTI/SLTU (Set If Less-than) instruction

- Syntax: SLT Rd,Rs,Rt or SLT Rd,Rs,imm

- If Rs < Rt then Rd = 1, else Rd = 0

- Use appropriate BNE/BEQ instruction to infer relationship

| Branch if | SLT             | BNE/BEQ       |

|-----------|-----------------|---------------|

| \$2 < \$3 | SLT \$1,\$2,\$3 | \$1,\$0,label |

| \$2 ≤ \$3 | SLT \$1,\$3,\$2 | \$1,\$0,label |

| \$2 > \$3 | SLT \$1,\$3,\$2 | \$1,\$0,label |

| \$2 ≥ \$3 | SLT \$1,\$2,\$3 | \$1,\$0,label |

Range of Branching **Branch Machine Code Format**  How far away can you branch? Branch instructions use the I-Type Format Largest positive 16-bit number: 0x 6-bits 5-bits 5-bits 16-bits Largest negative 16-bit number: 0x opcode rs (src1) rt (src2) Signed displacement - 16-bit range => ±32KB • Operation: PC = PC + {disp., 2'b00} Displacement is 16-bits concatenated with two 0's Displacement notes — 18-bit range => МЕМ - Displacement is the value that should be 0xA140 add added to the PC so that it now points to the 0xA144 sub desired branch location 0xA148 bne Processor appends two 0's to end of disp. 0xA14c or since all instructions are 4-byte words 0xA150 Iw • Essentially, displacement is in units of words 0xA154 beq

USC Viterbi

## **Jump Instructions**

- Instruction format: J-Type

- Jumps provide method of branching beyond range of 16-bit displacement

- Syntax: J label/address

- Operation: PC = address

- Address is appended with two 0's just like branch displacement yielding a 28bit address with upper 4-bits of PC unaffected

|                                 |                             | 0x1000001          |        |  |

|---------------------------------|-----------------------------|--------------------|--------|--|

| 6-bits                          | 6-bits 26-bits              |                    |        |  |

| opcode                          |                             | Jump address       |        |  |

|                                 | Sample                      | e Jump instruction |        |  |

| 0x8                             | 0x8                         |                    |        |  |

|                                 |                             | Old PC             |        |  |

|                                 | PC before execution of Jump |                    |        |  |

| 4-bits                          | 26-bits                     |                    | 2-bits |  |

| Old PC<br>[31:28]               |                             | Jump address       | 00     |  |

| New PC after execution of Jump` |                             |                    |        |  |

|                                 |                             | 0x84000004         |        |  |

**Jump Register**

- 'jr' instruction can be used if a full 32-bit jump is needed or variable jump address is needed

- Syntax: JR rs

- Operation: \_\_\_\_\_ = R[s]

- R-Type machine code format

- Usage:

- Can load rs with an immediate address

- Can calculate rs for a variable jump (class member functions, switch statements, etc.)

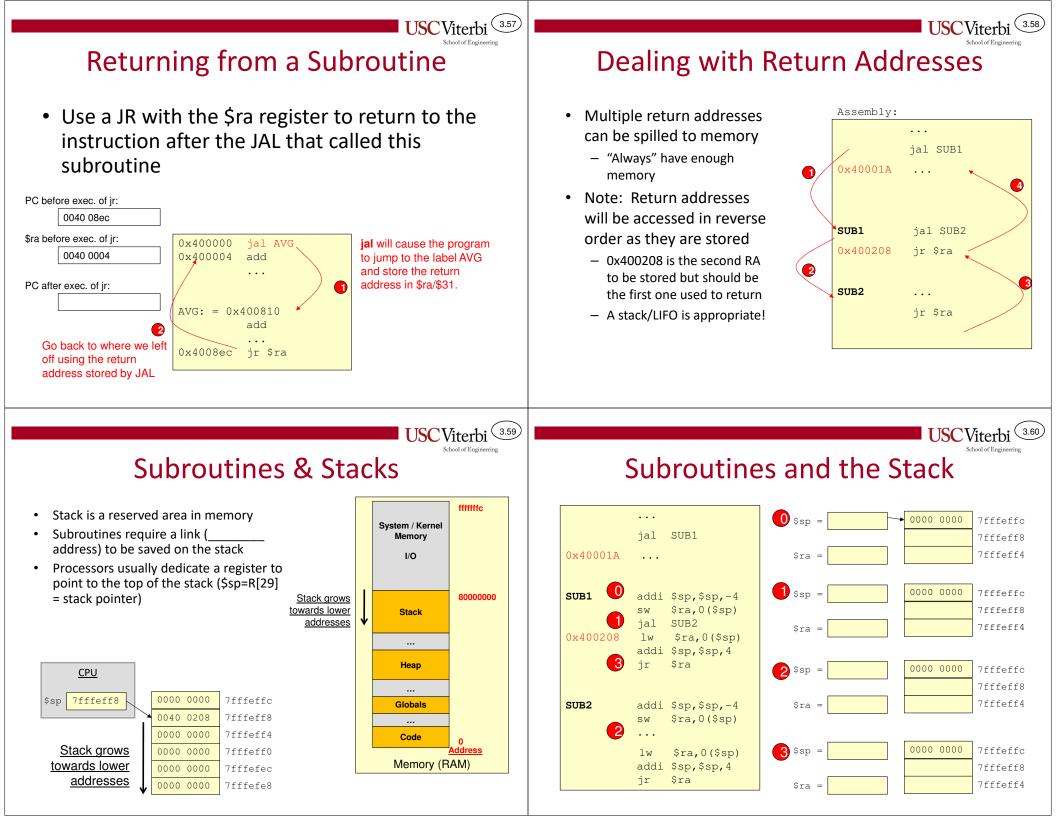

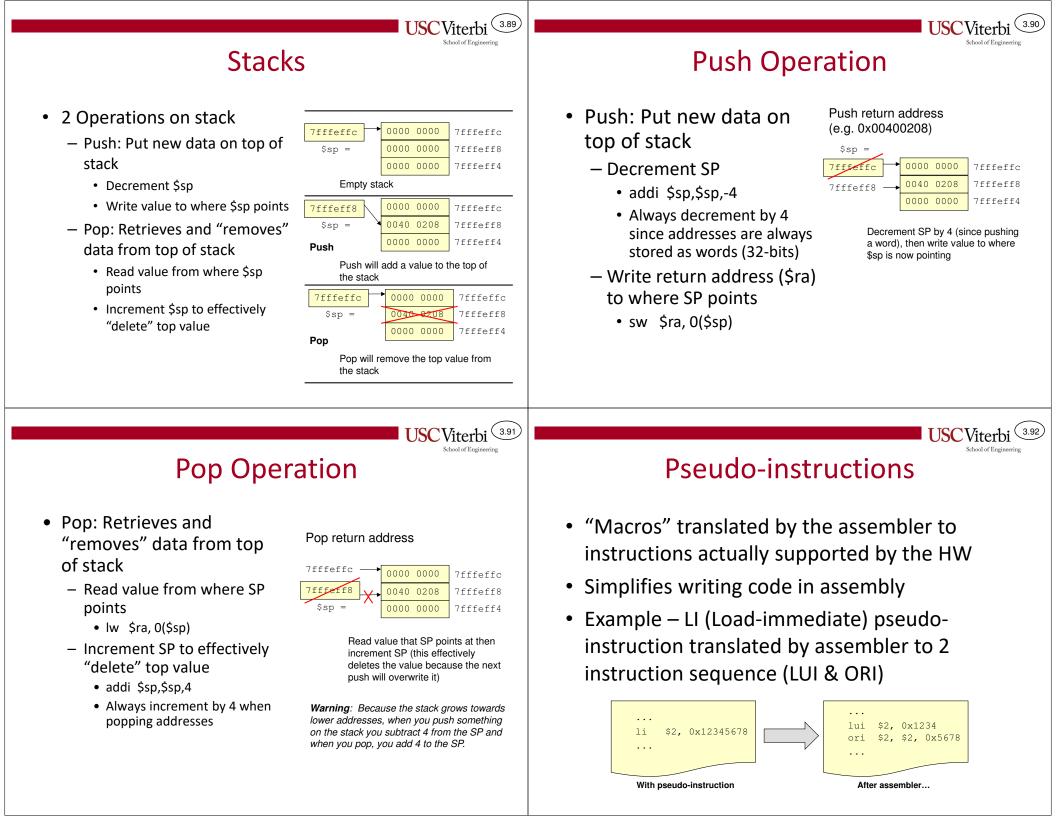

#### **Stack Facts Stack Facts** Stack grows in the Stack Pointer points to • When you pop, first you • When you push do direction of: the (top/bottom) of the then you you... stack Decreasing Addresses Increment the SP Increasing address Decrement the SP Stack Pointer Register • Stack is a (LIFO / FIFO) points to the • When you push do you data structure. - Top-most FILLED location First update the SP and then place data Next FREE location above the top-most Place data then update filled location SP Recall: · The stack grows downward The stack pointer points at the top OCCUPIED element on the stack. USC Viterbi (3.63) Subroutines Calling Subroutines **Stack Balancing** Stack shall be balanced: Nested subroutines make the stack (grow / shrink) because more number of push and pops (stack pointer values / return addresses) are Pops shall be performed in order stored on the stack as corresponding pushes Recursive subroutines make the stack (grow / shrink)

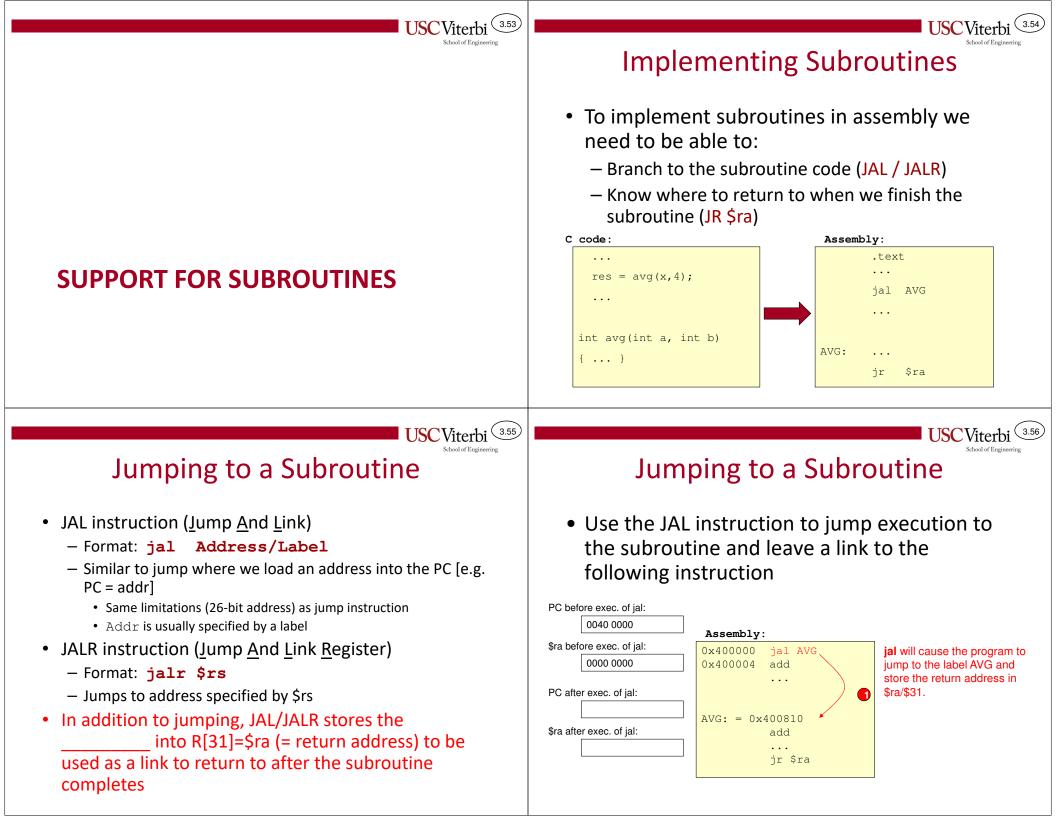

#### Subroutines and the Stack

- When writing native assembly, programmer must add code to manage return addresses and the stack

- At the beginning of a routine (PREAMBLE)

- Push \$ra (produced by 'jal') onto the stack addi \$sp, \$sp, -4 sw \$ra, 0 (\$sp)

- Execute subroutine which can now freely call other routines

- At the end of a routine (POSTAMBLE)

- Pop/restore \$ra from the stack

- lw \$ra,0(\$sp)

addi \$sp,\$sp,4

jr \$ra

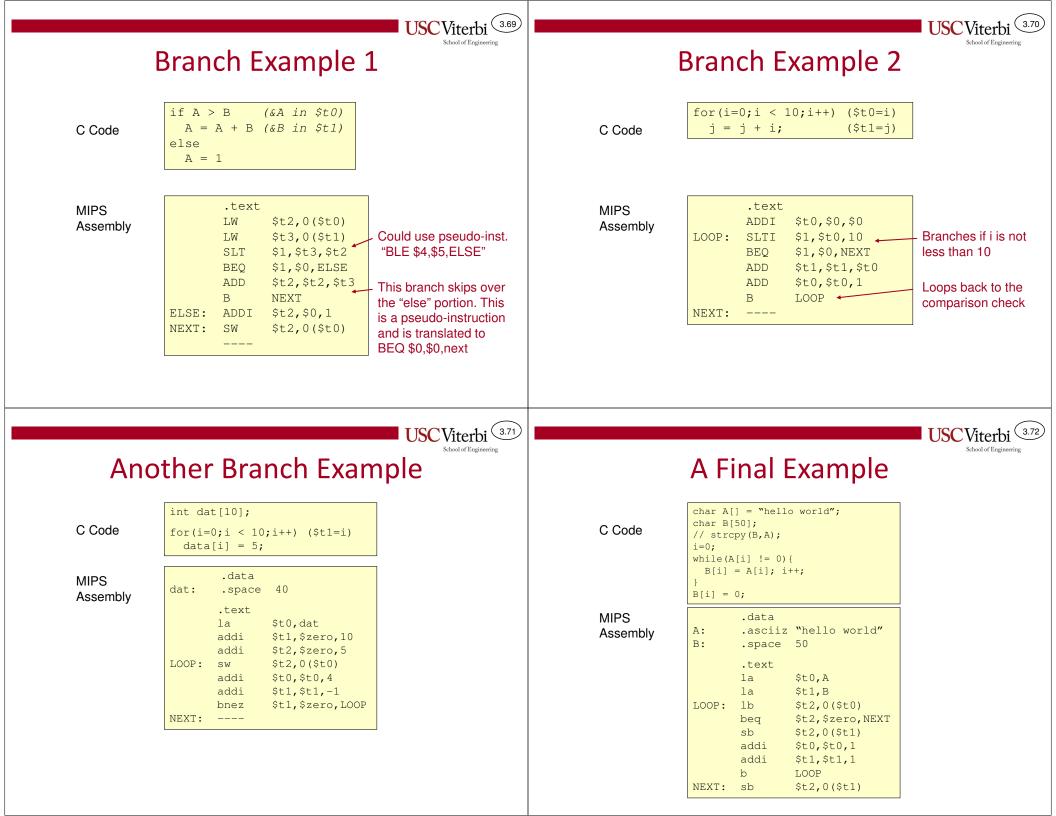

## Translating HLL to Assembly

#### • HLL variables are simply locations in memory

- A variable name really translates to an address in assembly

| C operator                   | Assembly                                                                                                           | Notes                                                         |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|

| int x,y,z;<br><br>x = y + z; | LUI \$8, 0x1000<br>ORI \$8, \$8, 0x0004<br>LW \$9, 4(\$8)<br>LW \$10, 8(\$8)<br>ADD \$9,\$9,\$10<br>SW \$9, 0(\$8) | Assume x @ 0x10000004<br>& y @ 0x10000008<br>& z @ 0x1000000C |  |

| char a[100];<br><br>a[1];    | LUI \$8, 0x1000<br>ORI \$8, \$8, 0x000C<br>LB \$9, 1(\$8)<br>ADDI \$9,\$9,-1<br>SB \$9,1(\$8)                      | Assume array 'a' starts @<br>0x1000000C                       |  |

USC Viterbi (3.67)

USC Viterhi (3.65)

#### Translating HLL to Assembly

| C operator                                               | Assembly                                                                                                                                              | Notes                                       |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| int dat[4],x;<br><br>x = dat[0];<br>x += dat[1];         | LUI \$8, 0x1000<br>ORI \$8, \$8, 0x0010<br>LW \$9, 0(\$8)<br>LW \$10, 4(\$8)<br>ADD \$9,\$9,\$10<br>SW \$9, 16(\$8)                                   | Assume dat @ 0x10000010<br>& x @ 0x10000020 |

| unsigned int y;<br>short z;<br>y = y / 4;<br>z = z << 3; | LUI \$8, 0x1000<br>ORI \$8, \$8, 0x0010<br>LW \$9, 0(\$8)<br>SRL \$9, \$9, 2<br>SW \$9, 0(\$8)<br>LH \$9, 4(\$8)<br>SLA \$9, \$9, 3<br>SH \$9, 4(\$8) | Assume y @ 0x10000010 &<br>z @ 0x10000014   |

Translating HLL to Assembly

USC Viterbi (3.68)

| C operator                                          | Assembly          |                                                                                                                                                                                                        |

|-----------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| int dat[4],x=0;<br>for(i=0;i<4;i++)<br>x += dat[i]; | DAT:<br>X:<br>LP: | .space 16<br>.long 0<br>LA \$8, DAT<br>ADDI \$9,\$0,4<br>ADD \$10,\$0,\$0<br>LW \$11,0(\$8)<br>ADD \$10,\$10,\$11<br>ADDI \$8,\$8,4<br>ADDI \$9,\$9,-1<br>BNE \$9,\$0,LP<br>LA \$8,X<br>SW \$10,0(\$8) |

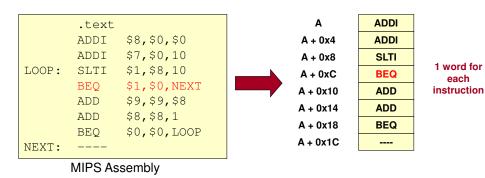

## Logical Operations

- Logic operations are often used for "bit" fiddling

- Change the value of 1-bit in a number w/o affecting other bits

- C operators: & = AND, | = OR, ^ = XOR, ~ = NOT

- Examples (Assume an 8-bit variable, v)

- Set the LSB to '0' w/o affecting other bits

- v = v & 0xfe;

- Check if the MSB = '1' regardless of other bit values

if(v & 0x80) { code }

- Set the MSB to '1' w/o affecting other bits

- v = v | 0x80;

- Flip the LS 4-bits w/o affecting other bits

- v = v ^ 0x0f;

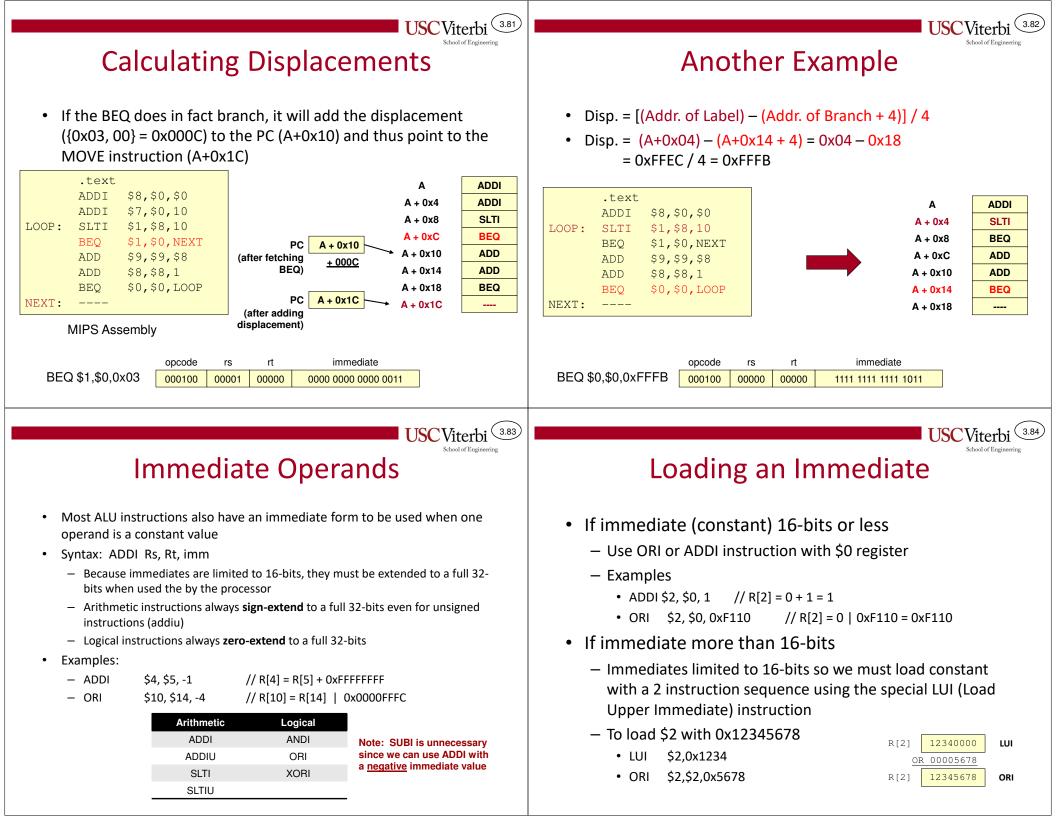

## **Calculating Branch Displacements**

- To calculate displacement you must know where instructions are stored in memory (relative to each other)

- Don't worry, assembler finds displacement for you...you just use the label

|       | .text |              | A        | ADDI | ]                  |

|-------|-------|--------------|----------|------|--------------------|

|       | ADDI  | \$8,\$0,\$0  | A + 0x4  | ADDI |                    |

|       | ADDI  | \$7,\$0,10   | A + 0x8  | SLTI | 1                  |

| LOOP: | SLTI  | \$1,\$8,10   | A + 0xC  | BEQ  | 1 word for<br>each |

|       | BEQ   | \$1,\$0,NEXT | A + 0x10 | ADD  | instruction        |

|       | ADD   | \$9,\$9,\$8  | A + 0x14 | ADD  | -                  |

|       | ADD   | \$8,\$8,1    | A + 0x18 | BEQ  |                    |

|       | BEQ   | \$0,\$0,LOOP | A + 0x1C |      | -                  |

| NEXT: |       |              | A+0.1C   |      | ]                  |

| -     |       | aambly       | -        |      |                    |

MIPS Assembly

USC Viterbi (3.79)

# **Calculating Displacements**

- Disp. = [(Addr. of Target) (Addr. of Branch + 4)] / 4

- Constant 4 is due to the fact that by the time the branch executes the PC will be pointing at the instruction after it (i.e. plus 4 bytes)

- Following slides will show displacement calculation for BEQ \$1,\$0,NEXT

# **Calculating Displacements**

- Disp. = [(Addr. of Target) (Addr. of Branch + 4)] / 4

- Disp. = (A+0x1C) (A+0x0C+ 4) = 0x1C 0x10 = 0x0C / 4

= 0x03

| LOOP: | .text<br>ADDI<br>ADDI<br>SLTI<br>BEQ<br>ADD | \$8,\$0,\$0<br>\$7,\$0,10<br>\$1,\$8,10<br><b>\$1,\$0,NEXT</b><br>\$9,\$9,\$8 | A<br>A + 0x4<br>A + 0x8<br>A + 0xC<br>A + 0x10<br>A + 0x14 | ADDI<br>ADDI<br>SLTI<br>BEQ<br>ADD | 1 word f<br>each<br>instructio |

|-------|---------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------|--------------------------------|

|       |                                             | \$9,\$9,\$8<br>\$8,\$8,1                                                      | A + 0x10<br>A + 0x14<br>A + 0x18                           | ADD<br>ADD<br>BEQ                  | instruction                    |

| NEXT: | BEQ<br>                                     | \$0,\$0,LOOP                                                                  | A + 0x18<br>A + 0x1C                                       |                                    |                                |

MIPS Assembly

# **Pseudo-instructions**

3.93

School of Engineering

**USC**Vit

| Pse       | Pseudo-instruction Act |                  | Actual Assembly                                                       |

|-----------|------------------------|------------------|-----------------------------------------------------------------------|

| NOT Rd,Rs |                        |                  | NOR Rd,Rs,\$0                                                         |

| NEG Rd,Rs |                        |                  | SUB Rd,\$0,Rs                                                         |

| LI        | Rt, immed.             | # Load Immediate | LUI Rt, {immediate[31:16], 16'b0}<br>ORI Rt, {16'b0, immediate[15:0]} |

| LA        | Rt, label              | # Load Address   | LUI Rt, {immediate[31:16], 16'b0}<br>ORI Rt, {16'b0, immediate[15:0]} |

| BLT       | Rs,Rt,Label            |                  | SLT \$1,Rs,Rt<br>BNE \$1,\$0,Label                                    |

Note: Pseudoinstructions are assembler-dependent. See MARS Help for more details.

#### Credits

3.94

These slides were derived from Gandhi Puvvada's EE 457 Class Notes