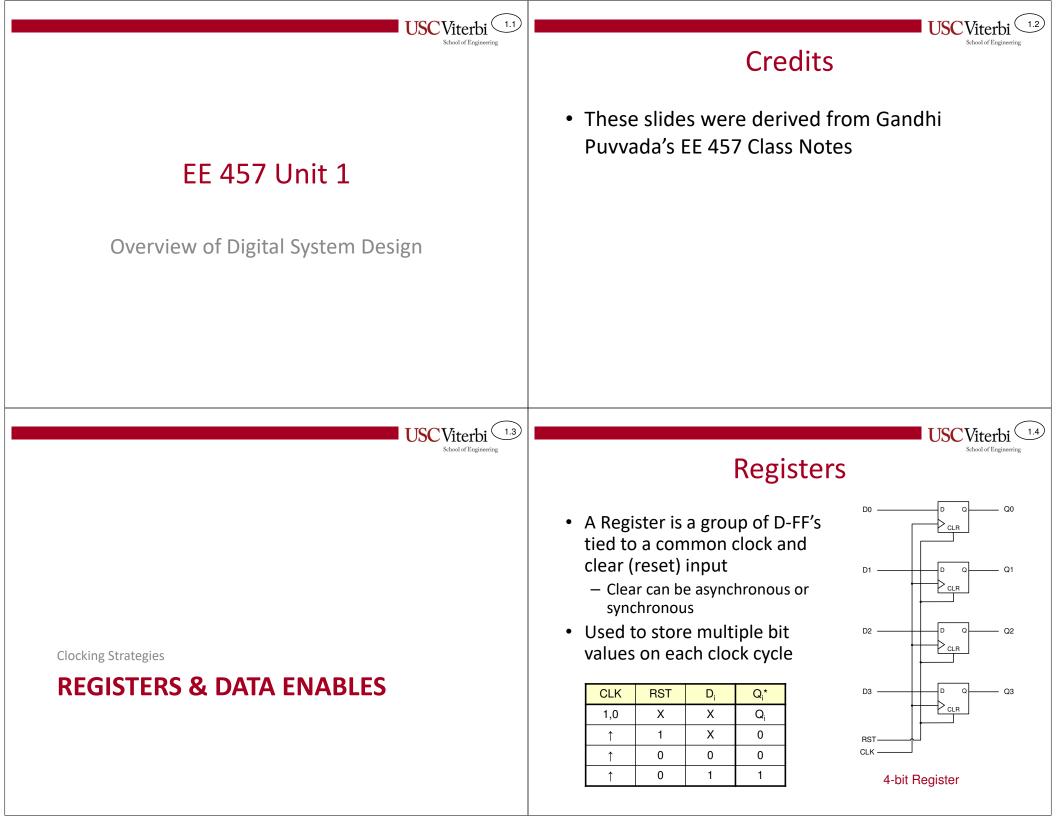

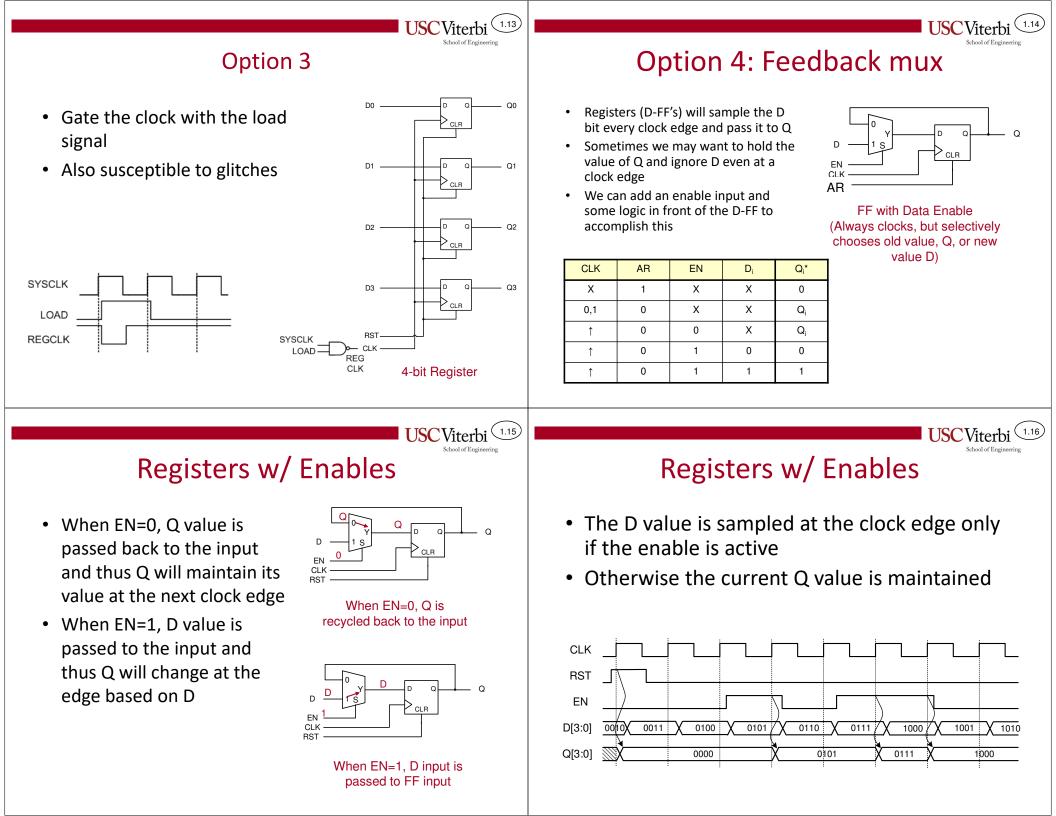

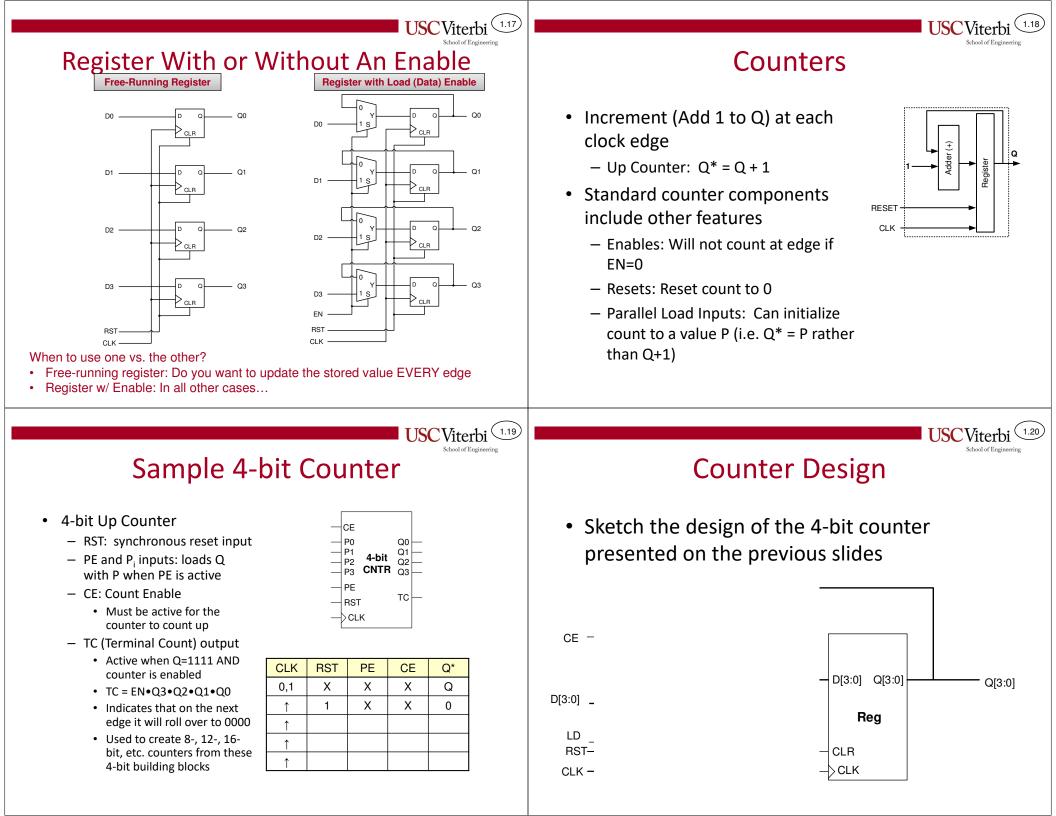

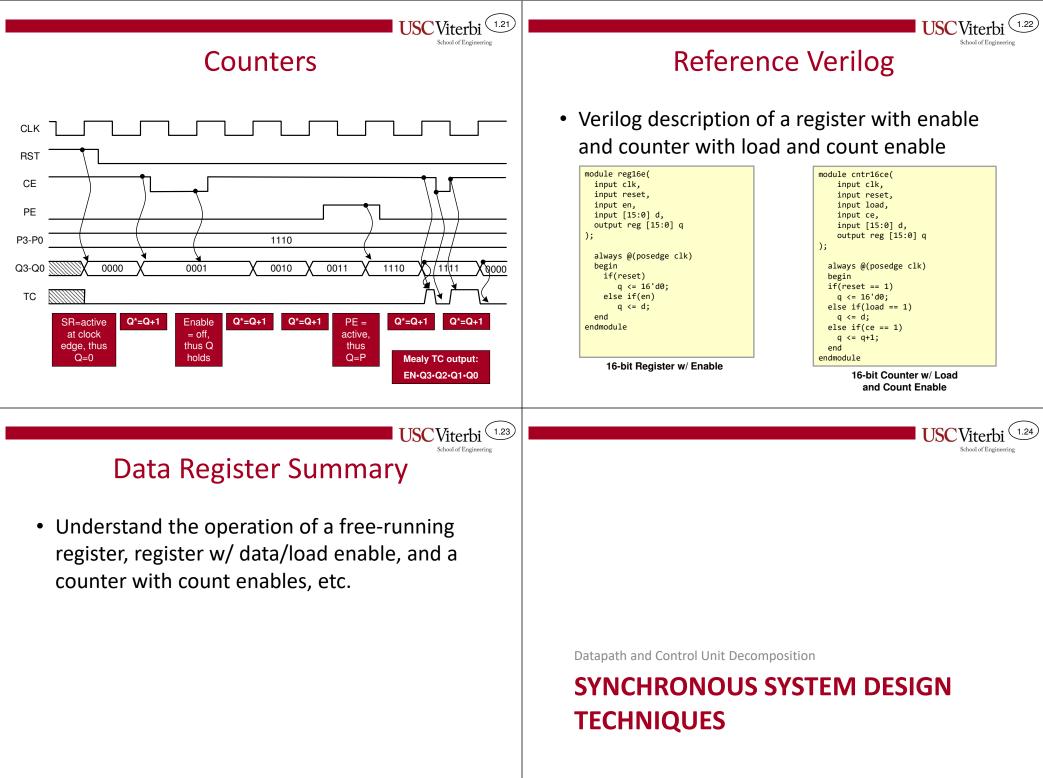

#### **Example:** Accumulator Synchronous vs. Asynchronous • Sum a time-based sequence of numbers • The set/preset and clear inputs can be built to be *synchronous* or asynchronous • A register usually stores a single logic value (i.e. a number) These terms refer to when the initialization takes place - Asynchronous Reset (AR): Initialization of Q takes effect immediately time regardless of the CLK 9.3.2 - Synchronous Reset (SR): Initialization of Q takes effect only at an edge Clock (clear must be active at the edge) Reset Synchronous Asynchronous Z1 St DO 4-bit Х 3 9 Clock Clock Adde Z2 DQ CLR CLR 5 Υ Z3 B2 DO Q's Q's Ζ ٥ 2 5 14 Clock Reset Synchronous SET or CLR Asynchronous SET or Register means the signal must be means Q will initialize as soon active at a clock edge before as the SET or CLR signal is Q will initialize activated 1.7 **USC**Viterbi School of Engineering Registers Selective Loading/Registering of Data • Whatever the D value is at the clock edge is sampled What if we only want a register and passed to the Q output until the next clock edge to capture data on selective clocks (and not on EVERY clock) D1 - Clocks are indicated with a "LOAD" CLE signal D2 CLK RST D3 SYSCLK D[3:0] 00/10 0100 0101 1001 1010 0011 0110 0111 1000 LOAD Q[3:0] ? 0000 1001 RS<sup>\*</sup> 0011 0100 0101 0110 0111 1000 CLK Want to load the register on the indicated 4-bit Register - On clock edge, D is passed to Q clock cycles and have it retain its value in the 4-bit Register other cycles

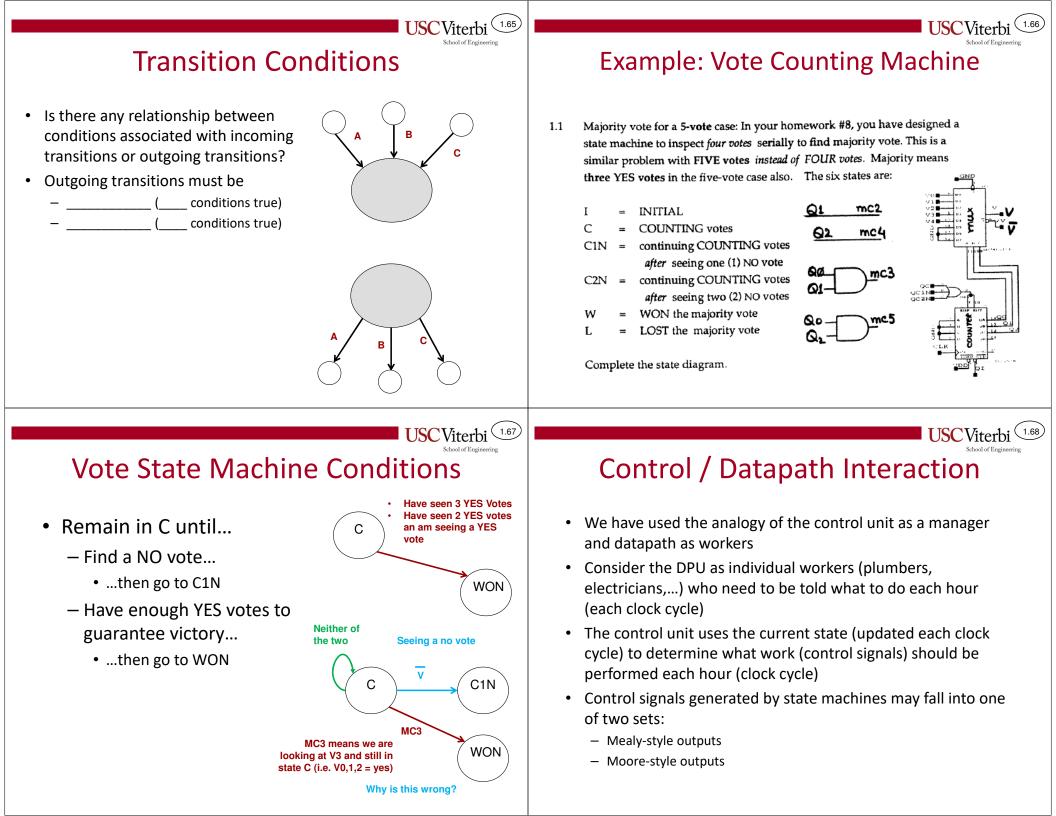

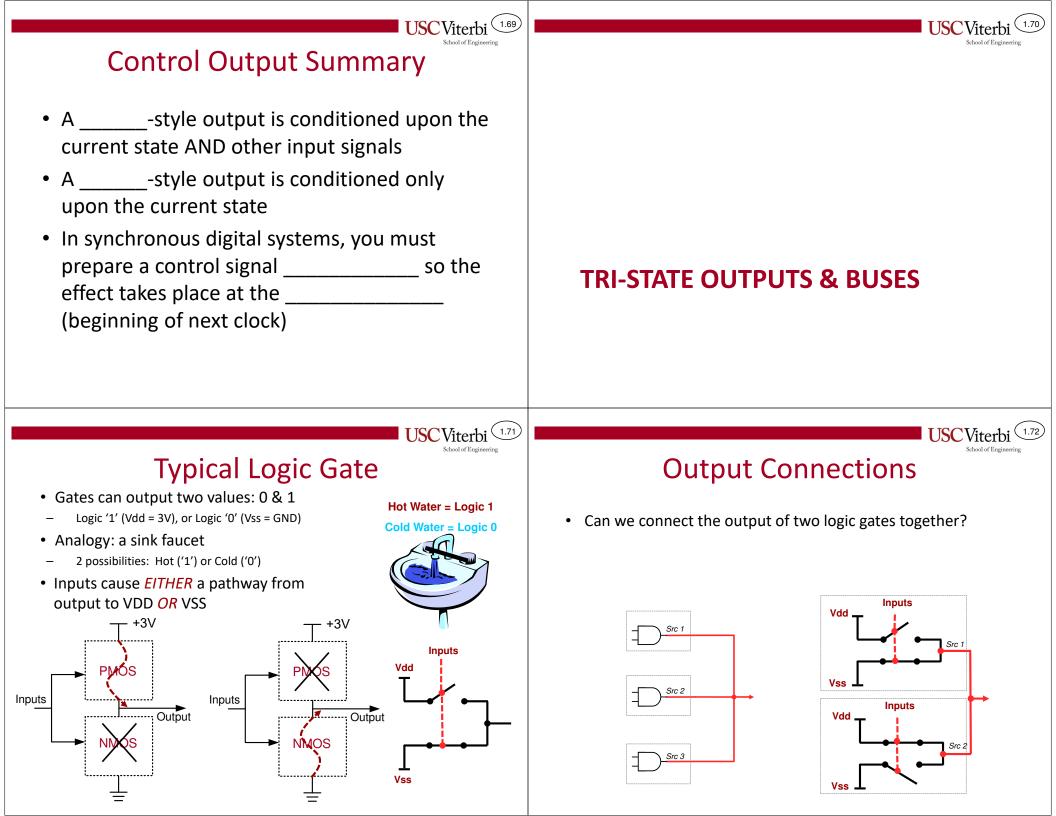

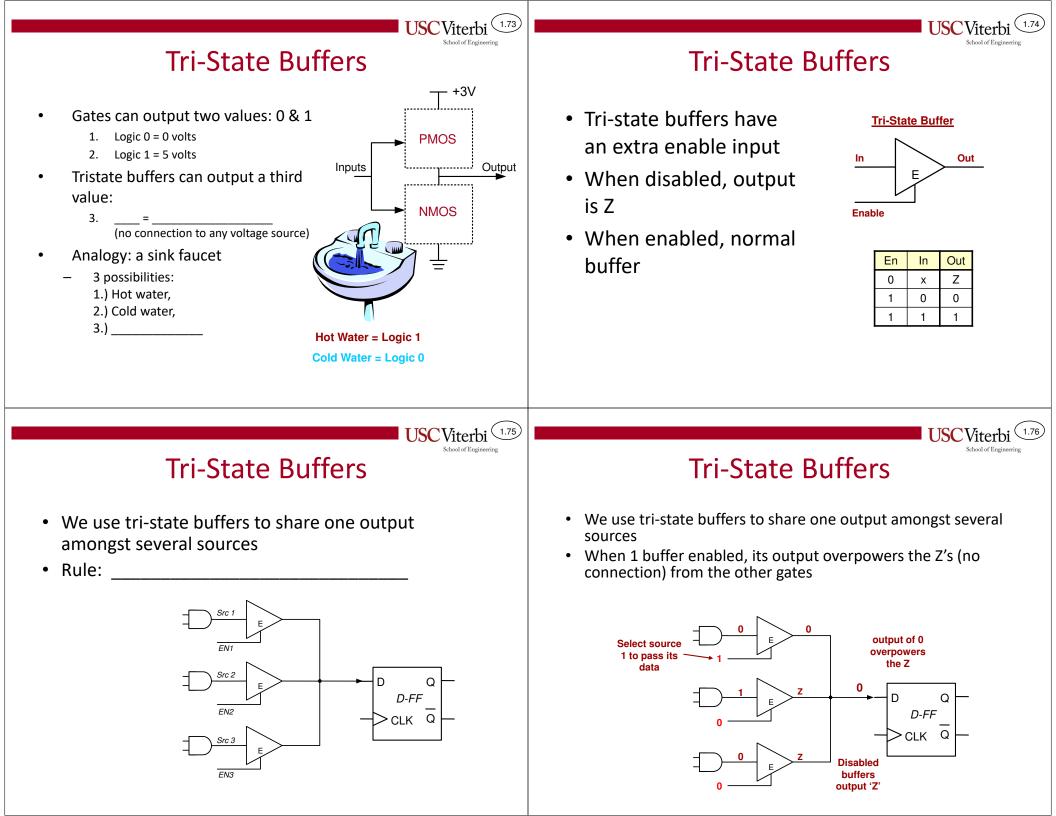

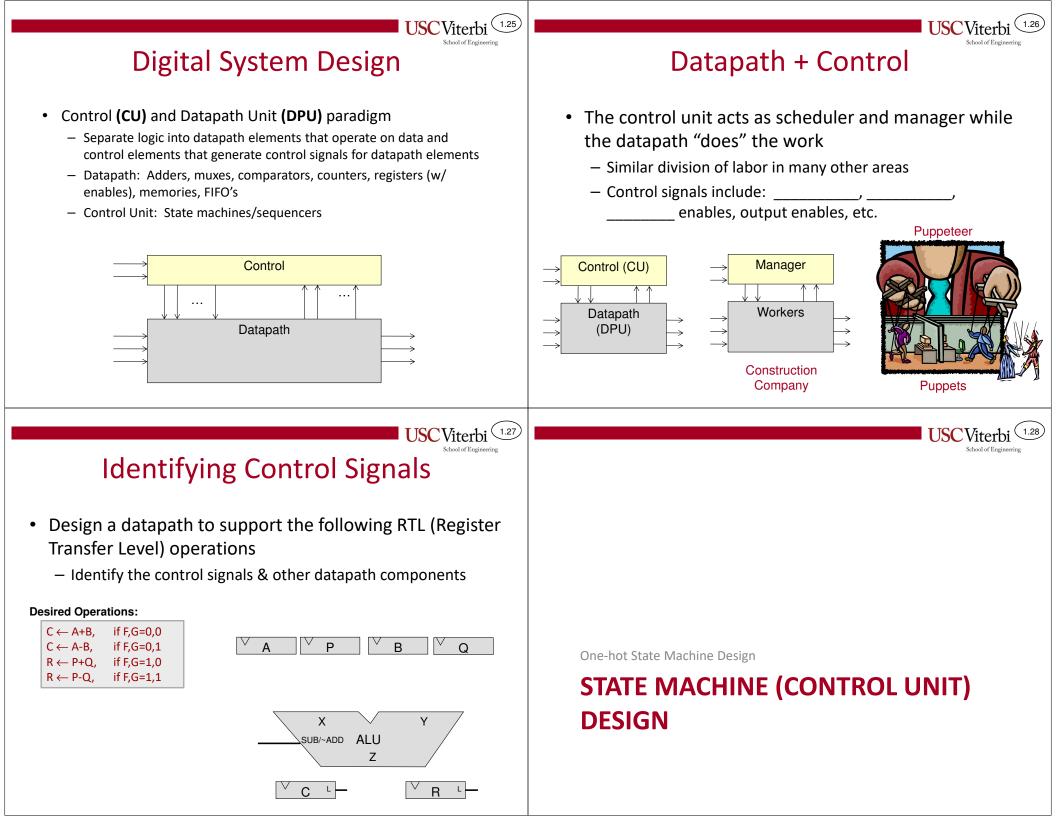

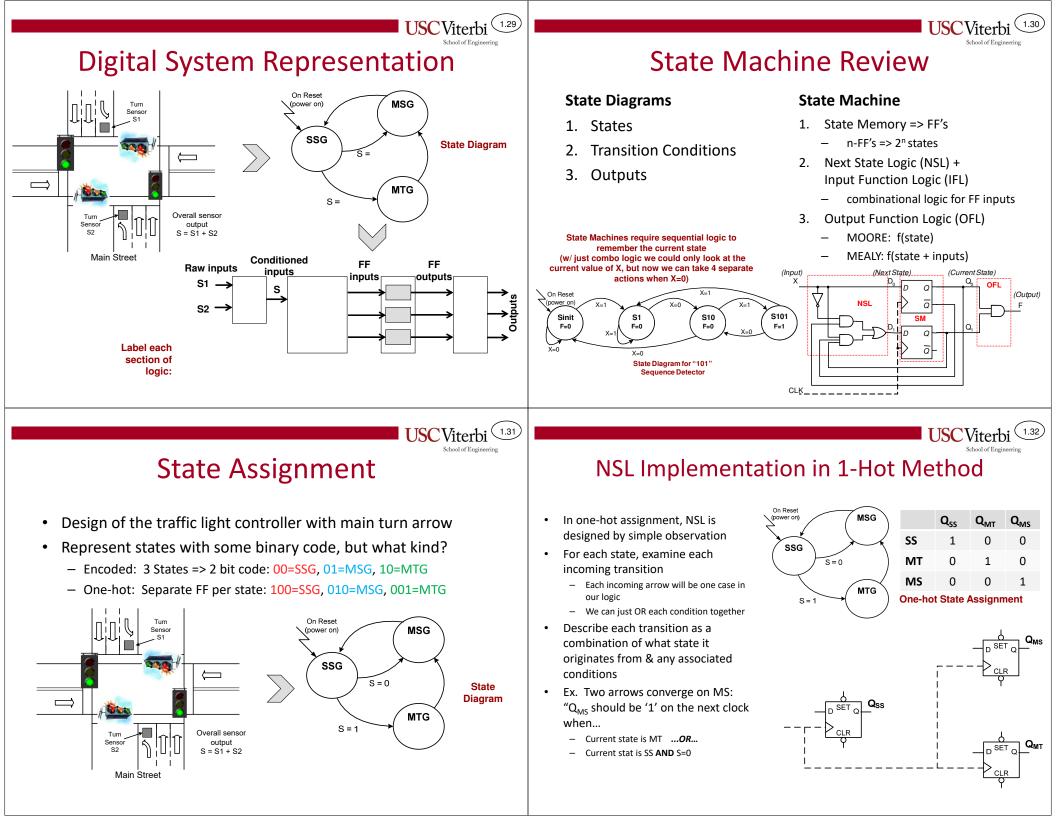

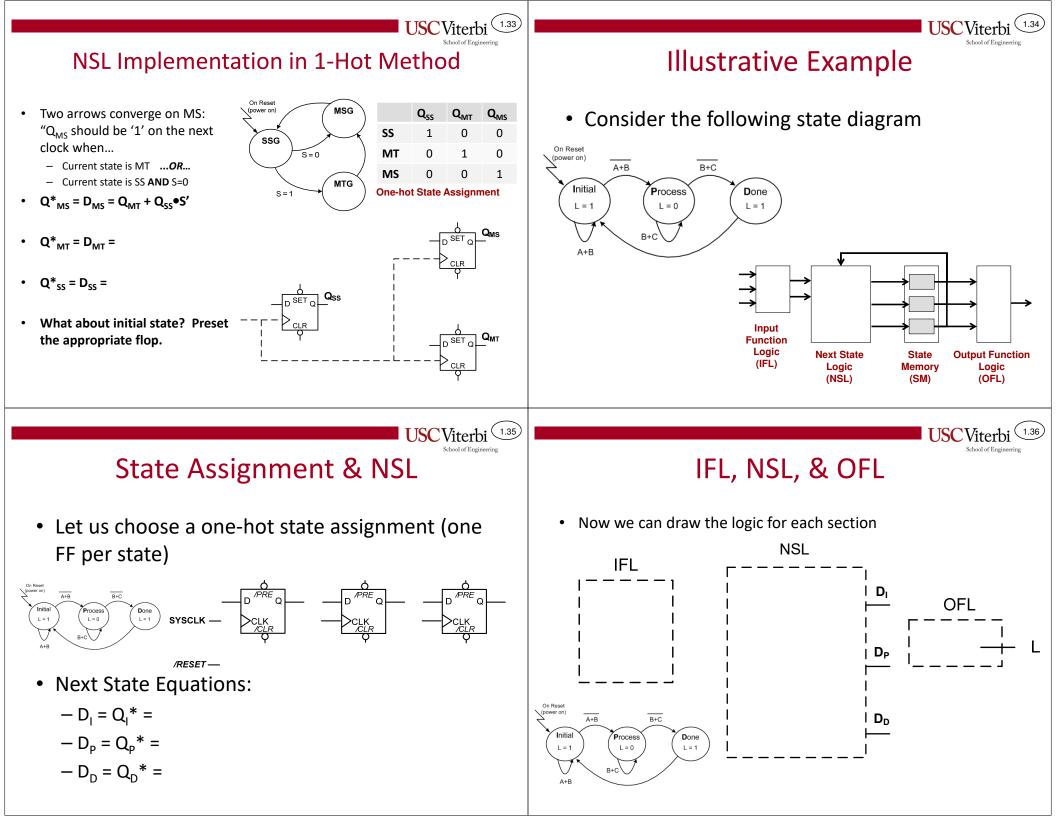

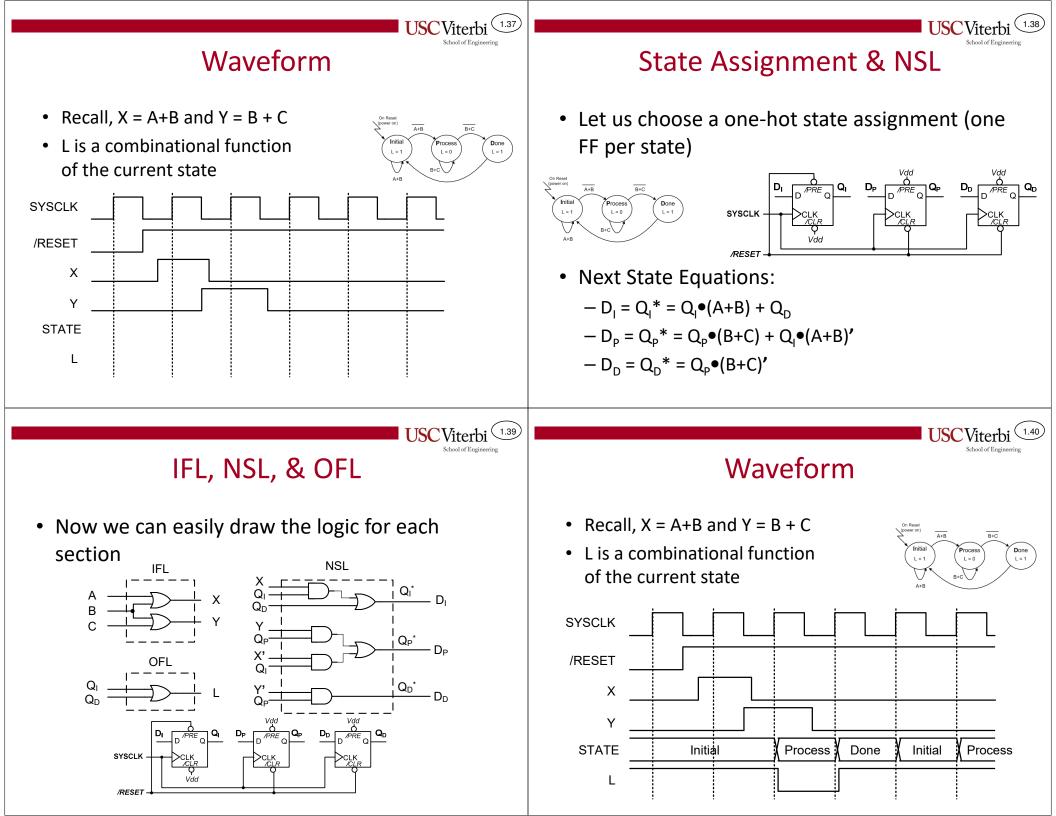

### 4 sections of state machine circuitry: In one-hot state encoding, a system with 5 states requires flip-flops (flip-flops per) • In an encoded state encoding, a system with 5 states requires flip-flops ( FF's for n states) • When designing the NSL for a state, enumerate the conditions associated with the (incoming/outgoing) transitions to that Mealy- vs. Moore-style outputs state STATE MACHINE OUTPUTS • To implement the power-on reset condition in a one-hot state encoding, connect the RESET signal to the \_\_\_\_\_ input for the FF associated with the initial state, and to the signals of the other FF(s). USC Viterbi (1.43) USC **Moore-Style Outputs** State Machine Outputs Moore-style outputs only depend on the current state State Machine outputs can be classified • Thus, they are valid in the clock cycle and *stay* according to how the outputs are produced nearly the entire Often requires extra states compared to Mealy-style implementations – If Outputs = f(current state, other inputs)... -Style The inputs do not feed into the OFL, thus Moore-Style inputs next current Next State Logic State Output – If Outputs = f(current state)... outputs state state State 1 Memory Function 7 = 1 $\mathbf{D}_{i}, \mathbf{J}_{i}/\mathbf{K}_{i},$ Qi (Flip-Logic -Style etc. Flops) SYSCIE Moore output **Depends on state** (State1) only clock

**State Machine Summary**

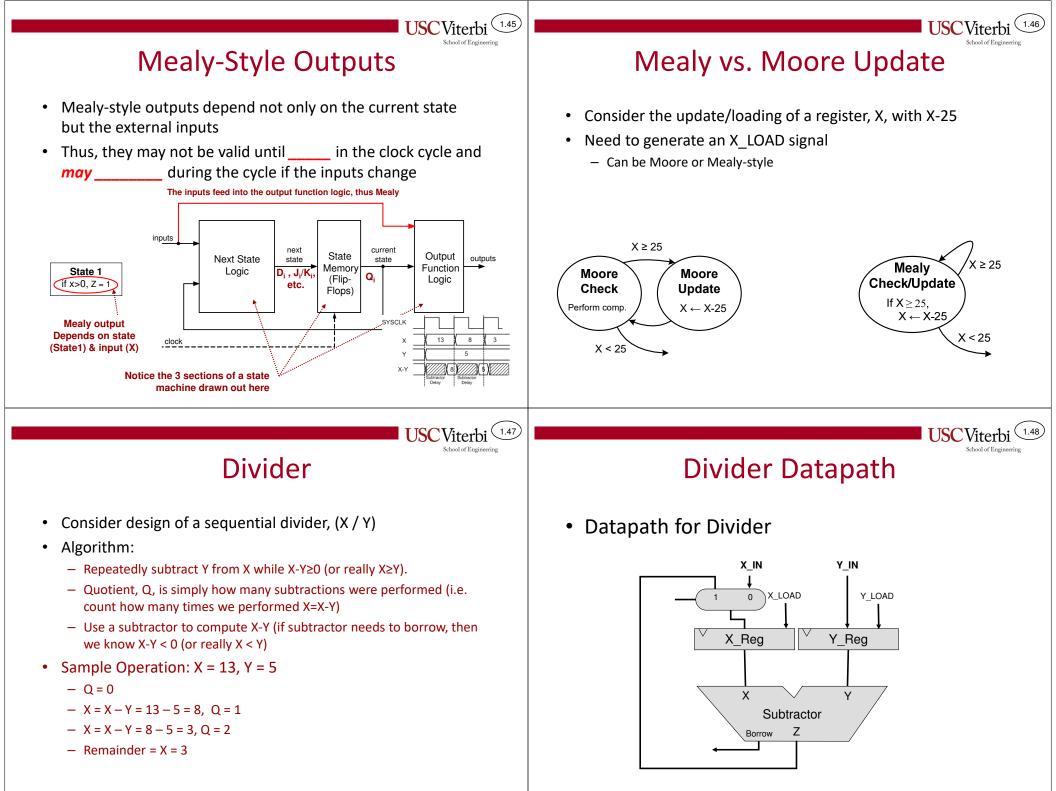

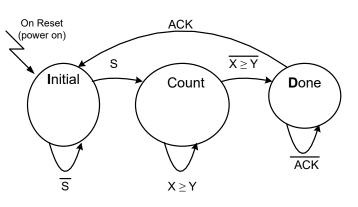

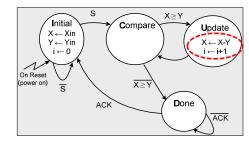

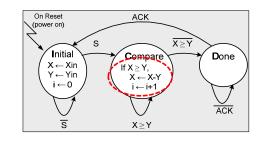

# Divider Control Unit

- Complete the state diagram

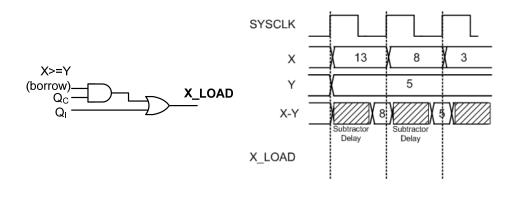

- What is the logic for X\_Load

# Mealy vs. Moore Comparison

## **Moore Implementation**

- We need to compare X with Y to determine if we should increment our quotient and update X

- If we want Moore-style enable and increment signals, we need a separate compare & update state

### **Mealy Implementation**

In a Mealy-style implementation we can compare and use the result to produce the enable and increment signals in the same clock

USC Viterbi School of Engineeri

( 1.51)

# Mealy Timing

In Mealy-style implementation, we must ensure the clock is long enough for control signals to be produced

# Control Signal Timing

• When identifying control signals in the datapath, be sure to consider if the signal should be valid

## -"During the clock"

- Must be valid shortly after the beginning of the clock (e.g. mux selects, etc.)

- Usually must be produced as Moore-style output or fast, Mealy output

# -"At the end of the clock"

- Must be valid by the end of the clock (e.g. register load enables)

- Can be produced by combo logic in datapath

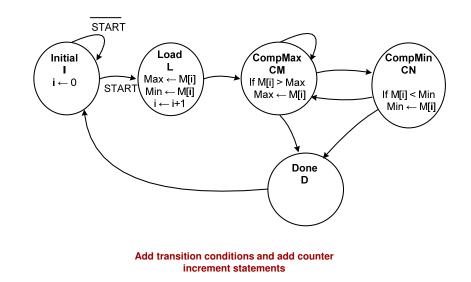

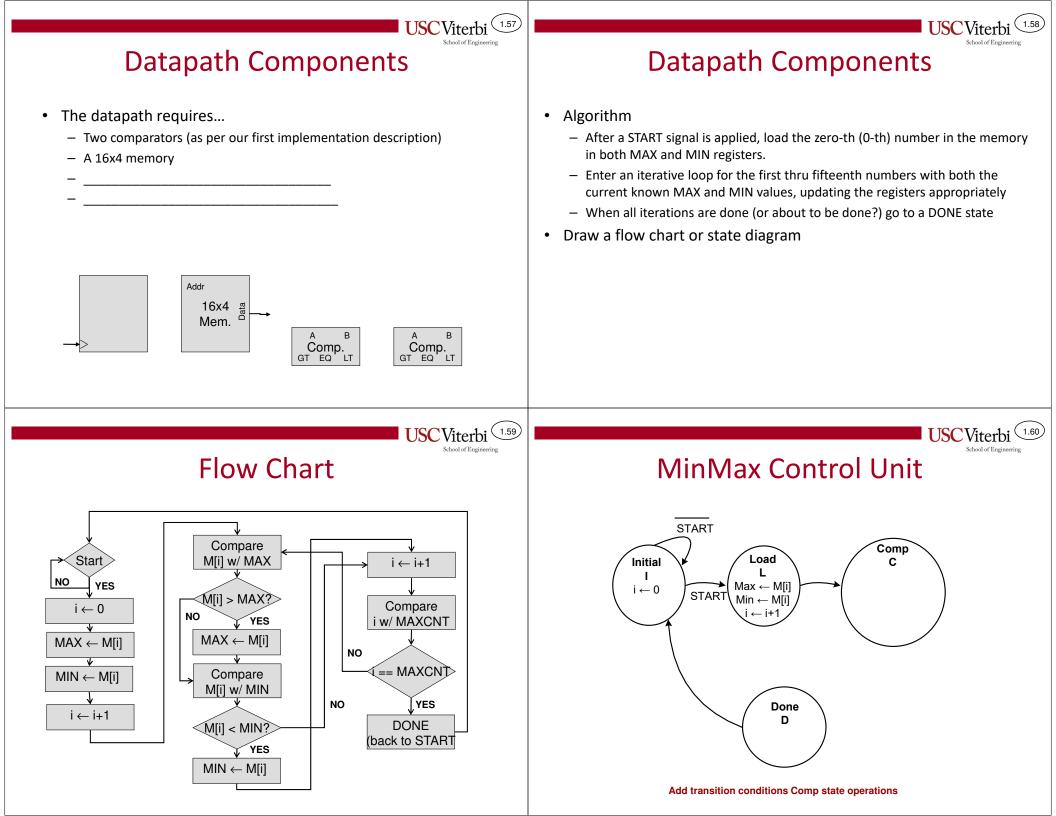

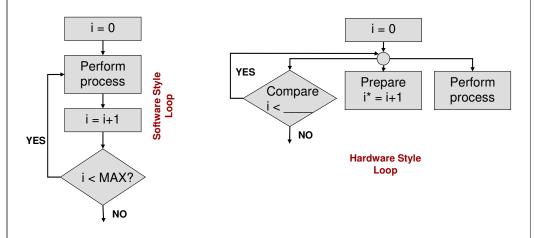

#### 1.53 **USC**Viterbi **Datapath Design Example Divider Datapath** Design a datapath to support the following RTL (Register • Datapath for Divider ٠ Transfer Level) operations X\_IN Y\_IN - Identify the control signals & other datapath components X LOAD Y LOAD 0 **Desired Operations:** $C \leftarrow A+B$ , if F,G=0,0 X Reg Y Reg $C \leftarrow A-B$ , if F,G=0,1 C $R \leftarrow P+Q$ , if F,G=1,0 $R \leftarrow P-Q$ , if F,G=1,1 Х Y Subtractor Х Y Ζ Borrow SUB/~ADD ALU Ζ V R С (1.55) **USC**Viterbi ( 1.56 **USC**Viterbi School of Engineering Min/Max Finder Description Sixteen 4-bit unsigned numbers are stored in a • 16x4 (16 rows/addresses of 4-bits each) • Iterate over all numbers and determine the 0 1 2 3 4 5 6 maximum (largest) and minimum (smallest) 30 51 52 53 54 10 21 data number • First implement assuming (2) 4-bit comparators are available int min = data[0]; • Repeat the implementation assuming (1) 4-bit int max = data[0]; for(int i=1; i < N; i++)</pre> comparator is available **MIN/MAX FINDER** if(data[i] < min)</pre> Remember in HW we try to perform as many ٠ min = data[i]; operations in parallel as possible to achieve if(data[i] > max) max = data[i]; speed (e.g. perform iteration counter increment in same clock as iteration) How many clocks do you think we need? •

# Control Signal Timing Example

- Consider the following statement of building a counter such that i increments

(i ← i+1) on each clock

- (During the clock / At the end of the clock) you enable the counter so that (during the clock / at the end of the clock) it actually increments

- Consider designing a minutes & seconds counter circuit with separate counters for each

- Option 1: After 60 seconds (during 61<sup>st</sup> second) enable the minutes counter

- Option 2: During the 60<sup>th</sup> second (after 59 seconds) enable the minutes counter

USC Viterbi (1.63)

# 1 Comparator Datapath

- The datapath now requires...

- One comparator

- A 16x4 memory

- (2) registers to store current min / max

- (1) 4-bit counter to counter iterations & address memory

## Early or Late?

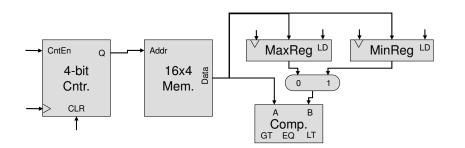

- Consider a counting loop to iterate MAX times

- In hardware we try to perform as many operations in parallel as possible

- To iterate MAX times, what should we compare with i?

**USC**Viterbi (

# 1-Comparator Implementation