Spiral 2-7

Capacitance, Delay and Sizing

## Learning Outcomes

**USC**Viterbi

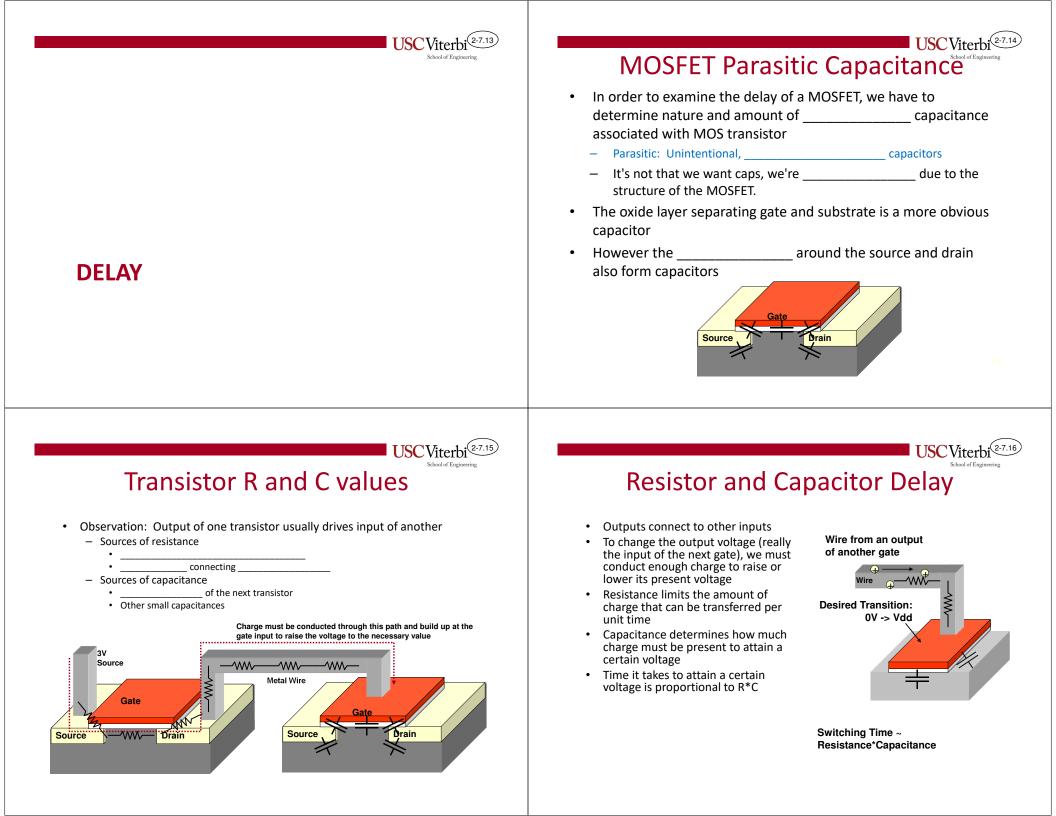

- I understand the sources of capacitance in CMOS circuits

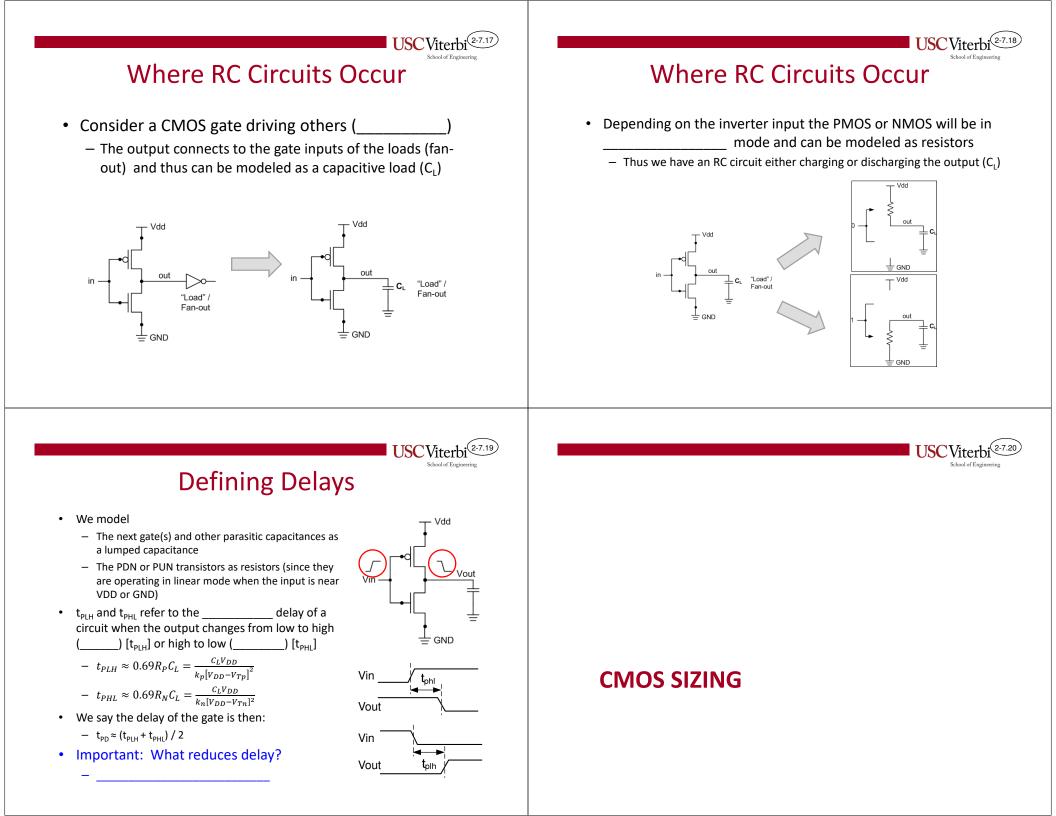

- I understand how delay scales with resistance, capacitance and voltage

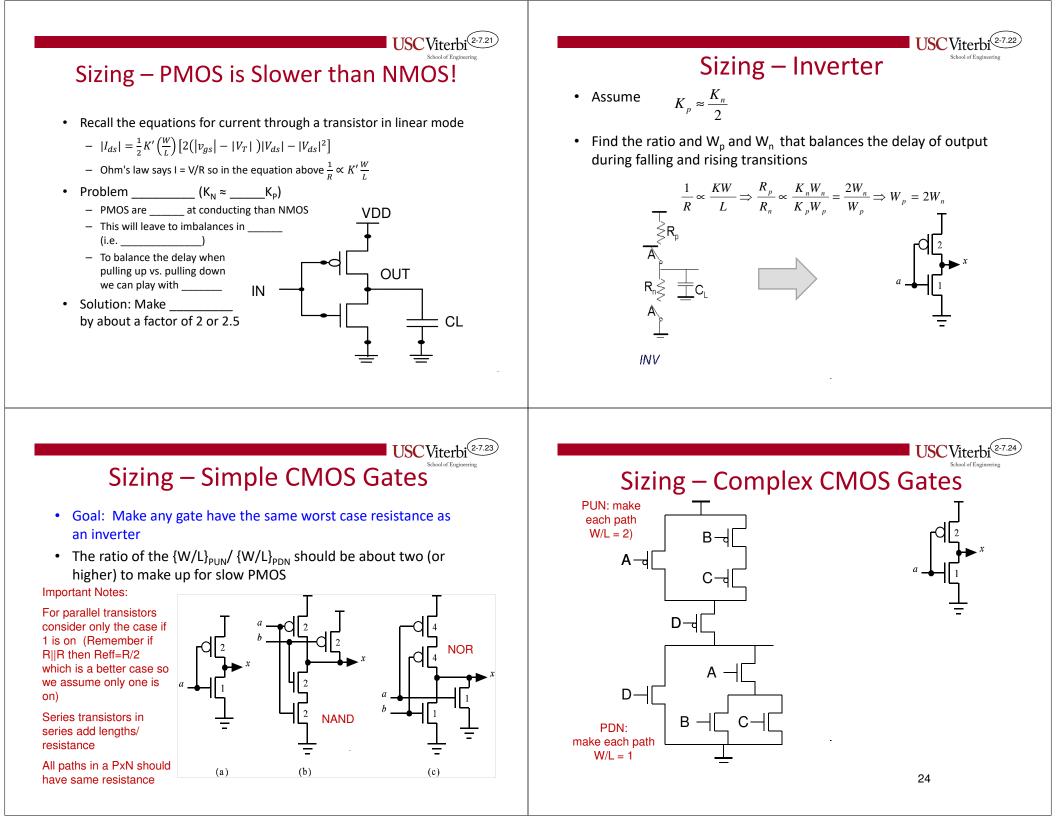

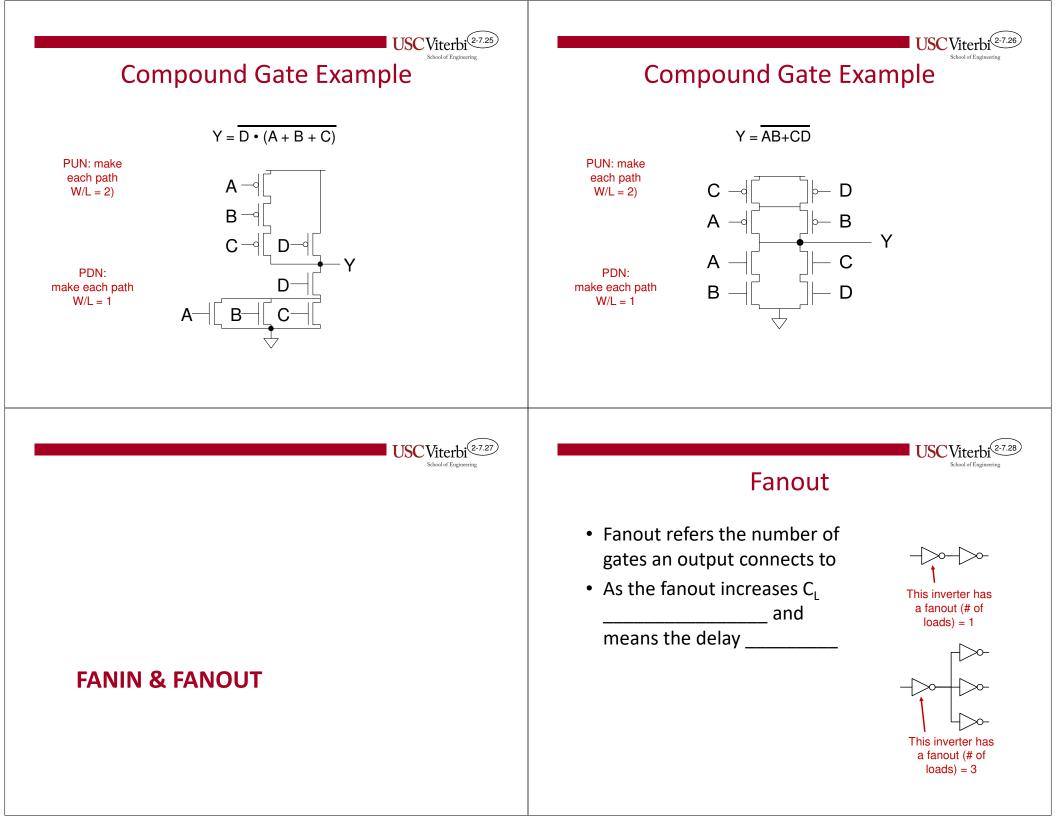

- I can determine appropriate width of PMOS and NMOS transistors based on the configuration of the transistors and given current conduction parameters

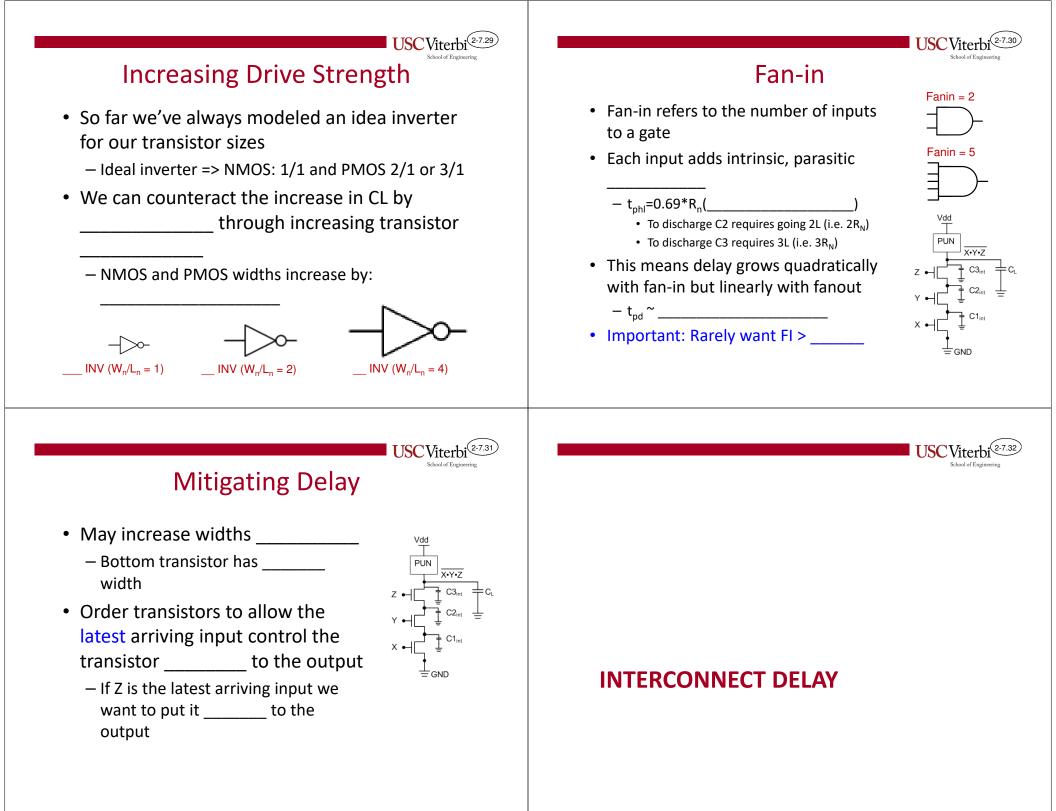

- I understand how fan-in and fan-out affect the delay of a circuit

- I understand how to use sizing to drive larger fan-out loads

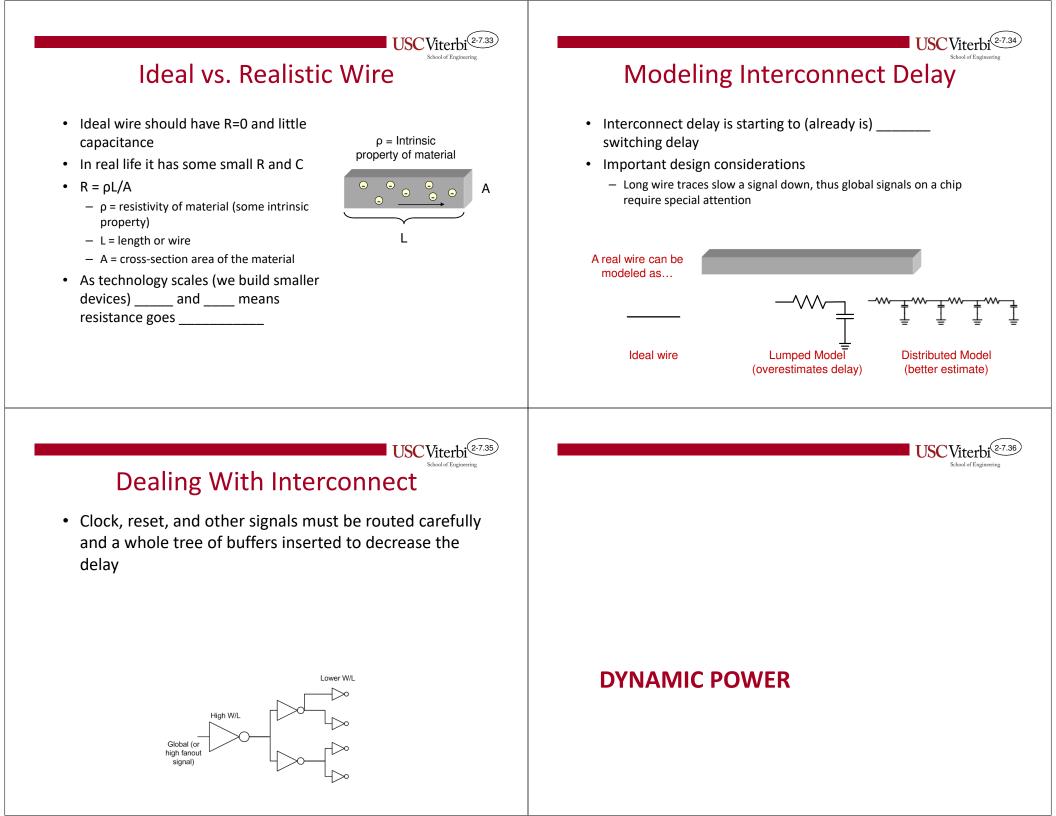

- I understand the sources of static and dynamic power consumption and how they are affect by changes in various parameters

capacitor)

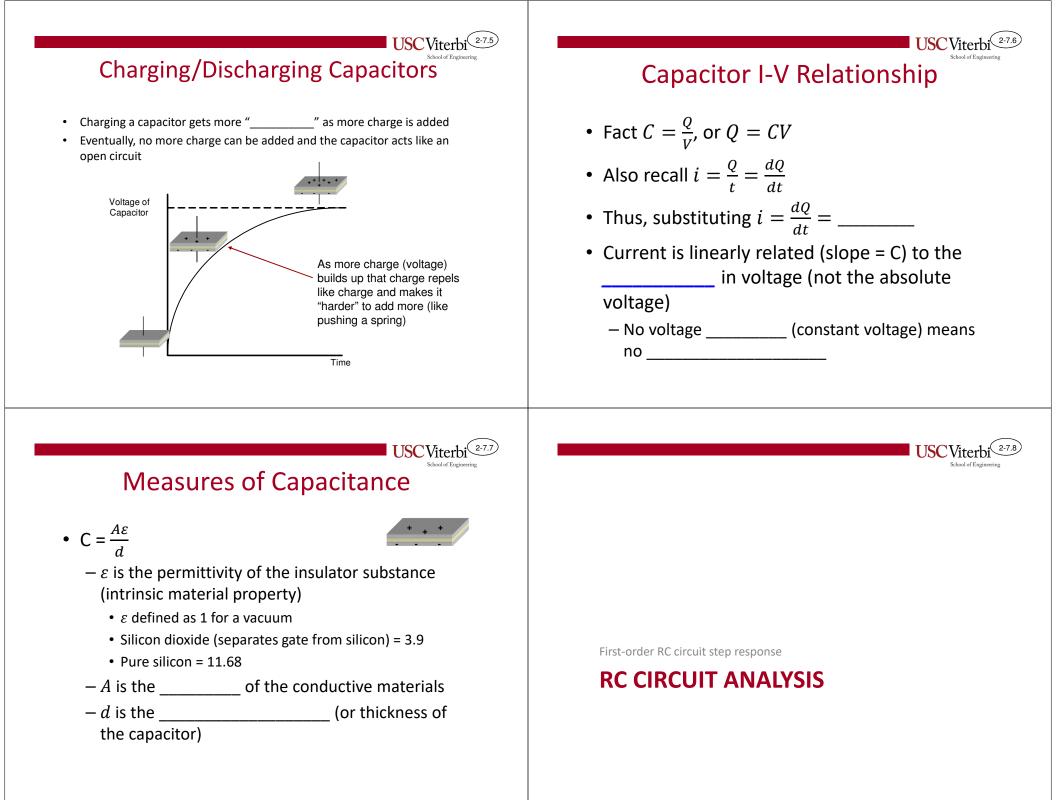

## **USC**Viter Capacitance Res. Conductive • Capacitors are formed by separating Material two \_\_\_\_\_\_ substances with an Capacitors " " charge Insulator Capacitance measures how much Material charge is needed to achieve a Connected to a source, charge will be stored certain voltage (electric potential) on the conductive plates creating a positive voltage between the conductive plates — C = Capacitance measured in Farads (F) Res. WHAT IS CAPACITANCE? To change the voltage at the capacitor we **Capacitor Schematic** must change the voltage (if we turn off the Symbol voltage source charge will drain off the

## Power

2-7.37

**USC**Viterbi

School of Engine

- Power consumption decomposed into:

- Static: Power constantly being dissipated (grows with # of transistors)

- Dynamic: Power consumed for switching a bit (1 to 0)

- $P_{DYN} = I_{DYN} * V_{DD} \approx \frac{1}{2}C_{TOT}V_{DD}^2 f$

- Recall, I = C dV/dt

- $V_{DD}$  is the logic '1' voltage, f = clock frequency

- Dynamic power favors parallel processing vs. higher clock rates

- V<sub>DD</sub> value is tied to f, so a reduction/increase in f leads to similar change in Vdd

- Implies power is proportional to f<sup>3</sup> (a cubic savings in power if we can reduce f)

- Take a core and replicate it 4x => 4x performance and 4x power

- Take a core and increase clock rate 4x => 4x performance and 64x power

- Static power

- Leakage occurs no matter what the frequency is

## Temperature

- Temperature is related to power consumption

- Locations on the chip that burn more power will usually run hotter

- Locations where bits toggle (register file, etc.) often will become quite hot especially if toggling continues for a long period of time

- Too much heat can destroy a chip

- Can use sensors to dynamically sense temperature

- Techniques for controlling temperature

- External measures: Remove and spread the heat

- Heat sinks, fans, even liquid cooled machines

- Architectural measures

- Throttle performance (run at slower frequencies / lower voltages)

- Global clock gating (pause..turn off the clock)

- None...results can be catastrophic

- Fun video to be played now!