# **Learning Outcomes**

- I understand the active-low signal convention and how to interface circuits that use both active-high and active-low signals

- I can take any state diagram and create a corresponding state machine using one-hot implementation by using one FF per state and creating the D-input circuit by converting each incoming transition arrow to a state into a logic gate and ORing them together

- I understand how to decompose an algorithm into states for each step and appropriate datapath units for each operator

### Spiral 2-3

Negative Logic One-hot State Assignment System Design Examples

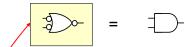

# **DeMorgan Equivalents**

#### **NEGATIVE (ACTIVE-LO) LOGIC**

# **Negative Logic**

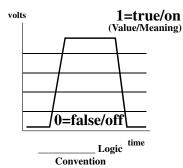

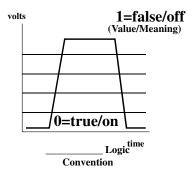

- Recall it is up to us humans to \_\_\_\_\_\_\_ to the two voltage levels

Thus, far we've used (unknowingly) the \_\_\_\_\_\_ logic convention where 1 means true and 0 means false

- In \_\_\_\_\_\_ logic 0 means true and 1 means false

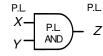

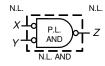

# Negative Logic 'AND' Function

# Traditional P.L. AND

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Traditional AND gate functionality assumes positive logic convention

# N.L. AND function

| X | Y | Z |

|---|---|---|

| 1 | 1 | 1 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 0 |

Given negative logic signals, we can invert to positive logic, perform the AND operation, then convert back to negative logic

# **N.L. AND = P.L. OR**

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

However, we then see that an OR gate implements the negative logic 'AND' function

### Why Active-low

### Negative Logic 'OR' Function

Traditional P.L. OR

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Traditional OR gate functionality assumes positive logic convention N.L. OR function

| X | Y | Z |

|---|---|---|

| 1 | 1 | 1 |

| 1 | 0 | 0 |

| 0 | 1 |   |

| 0 | 0 | 0 |

al OR gate

ity assumes

ve logic

ention

Given negative logic

signals, we can invert to

positive logic, perform the

OR operation, then convert

back to negative logic

N.L. OR = **P.L. AND**

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

However, we then see that an AND gate implements the negative logic 'OR' function

## **Negative Logic**

A negative logic OR function is equivalent to an AND gate

A negative logic AND function is equivalent to an OR gate

These are the preferred way of showing the N.L. functions because the inversion bubbles explicitly show where N.L. is being converted to P.L. and the basic gate schematics retain their meaning (when we see an AND gate we know we're doing some king of AND function with the bubbles indicating N.L.)

# i ve Active love

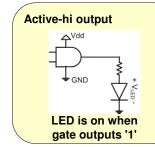

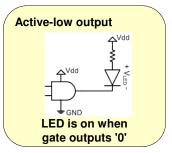

### Active-hi vs. Active-low

- Active-hi convention

- -1 = on/true/active

- -0 = off/false/inactive

- Active-low convention

- -0 = on/true/active

- -1 = off/false/inactive

- To convert between conventions

\_\_\_\_

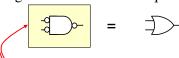

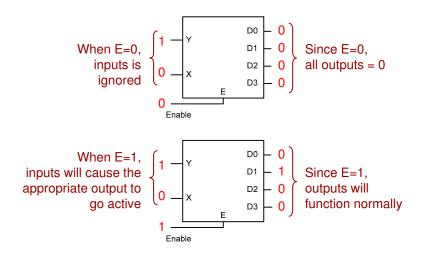

### **Enables**

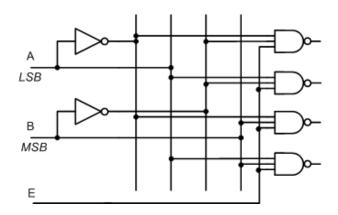

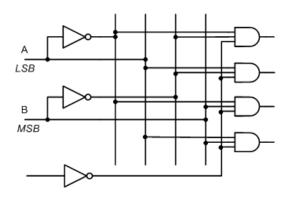

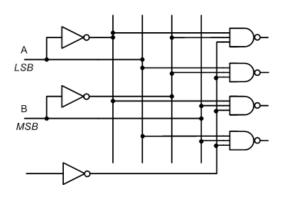

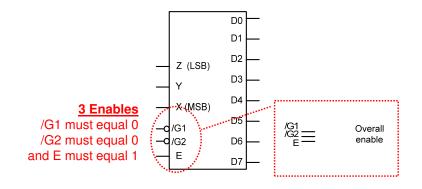

#### Decoder w/ Active Low Enable and Outputs

# **Active-Lo Outputs**

When E=inactive (inactive means 0), Outputs turn off (off means 1)

When E=active (active means 1), Selected outputs turn on (on means 0)

# USC Viterbi 2-3.14

#### Active-Lo Enable

When E=inactive (inactive means 1), Outputs turn off (off means 0)

When E=active (active means 0), Selected outputs turn on (on means 1)

#### Active-Lo Enable

When E=inactive (inactive means 1), Outputs turn off (off means 1)

When E=active (active means 0), Selected outputs turn on (on means 0)

• When a decoder has multiple enables, all enables \_\_\_\_\_ for the decoder to be enabled

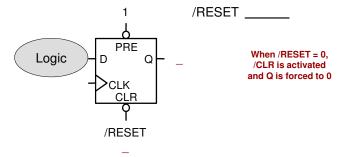

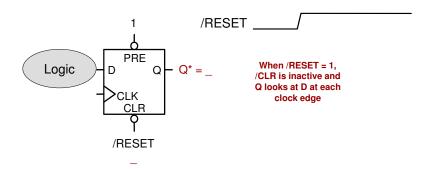

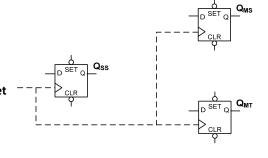

#### Active Low CLR and PRESET

- The reset signal might also be active low (0 = Reset, 1 = Normal operations)

- FFs can be made with active low /CLR & /PRE

Need to be able to initialize Q to a known value (0 or 1)

#### **ONE-HOT STATE ASSIGNMENT**

# **Encoded State Assignment Review**

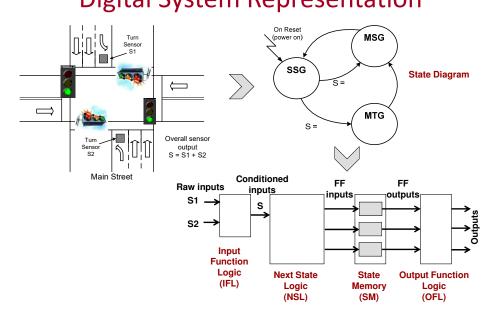

#### **State Diagrams**

- 1. States

- 2. Transition Conditions

- 3. Outputs

# State Machines require sequential logic to remember the current state (w/ just combo logic we could only look at the

State Diagram for "101

#### **State Machine**

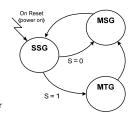

- 1. State Memory => FF's

- n-FF's => 2<sup>n</sup> states

- 2. Next State Logic (NSL) + Input Function Logic (IFL)

- combinational logic for FF inputs

- 3. Output Function Logic (OFL)

- MOORE: f(state)

- MEALY: f(state + inputs)

### State Assignment

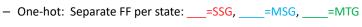

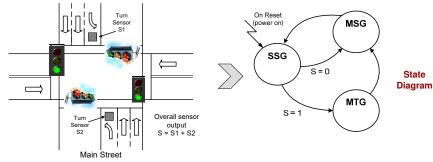

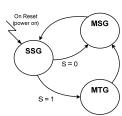

- Design of the traffic light controller with main turn arrow

- Represent states with some binary code, but what kind?

- Encoded: 3 States => \_\_\_\_\_ : \_\_=SSG, \_\_=MSG, \_\_=MTG

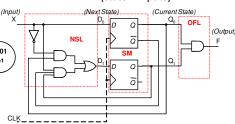

#### NSL Implementation in 1-Hot Method

- In one-hot assignment, NSL is designed by simple observation

- For each state, examine each transition

- Each incoming arrow will be one case in our logic

- We can just \_\_\_\_\_ each condition together

- Describe each transition as a combination of what state it originates from & any associated conditions

- - Current state is \_\_\_\_\_...OR...

- Current state is \_\_\_\_AND \_\_\_\_

|                          | $\mathbf{Q}_{\mathrm{ss}}$ | $\mathbf{Q}_{MT}$ | Q <sub>MS</sub> |  |  |  |

|--------------------------|----------------------------|-------------------|-----------------|--|--|--|

| SS                       | 1                          | 0                 | 0               |  |  |  |

| MT                       | 0                          | 1                 | 0               |  |  |  |

| MS                       | 0                          | 0                 | 1               |  |  |  |

| One-hot State Assignment |                            |                   |                 |  |  |  |

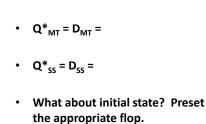

#### NSL Implementation in 1-Hot Method

- Two arrows converge on MS:

"Q<sub>MS</sub> should be '1' on the next

clock when...

- Current state is MT ...OR...

- Current stat is SS AND S=0

- $Q^*_{MS} = D_{MS} = Q_{MT} + Q_{SS} \bullet S'$

|        | $Q_{ss}$ | $\mathbf{Q}_{MT}$ | Q <sub>MS</sub> |

|--------|----------|-------------------|-----------------|

| SS     | 1        | 0                 | 0               |

| MT     | 0        | 1                 | 0               |

| MS     | 0        | 0                 | 1               |

| One-ho | t State  | Assignn           | nent            |

Array Multiplier (Combinational)

Add and Shift Method (Sequential)

#### **MULTIPLICATION TECHNIQUES**

#### **Combinational Multiplier Analysis**

| • | Large Area due to | bit adders |

|---|-------------------|------------|

|   |                   |            |

- n-1 because the first adder adds the first two partial products and then each adder afterwards adds one more partial product

- Propagation delay is in two dimensions

- proportional to \_\_\_\_\_

# **Multiplication Techniques**

- A multiplier unit can be

- Purely Combinational: Each partial product is produced in \_\_\_\_\_ and fed into an \_\_\_\_\_ of adders to generate the product

- Sequential and Combinational: Produce and add 1 partial product at a time (\_\_\_\_\_\_)

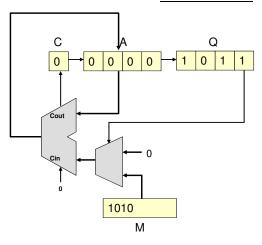

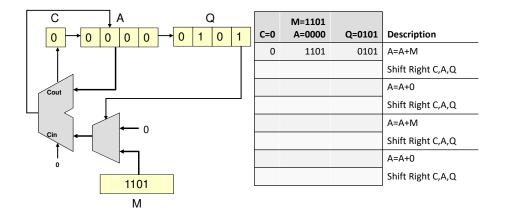

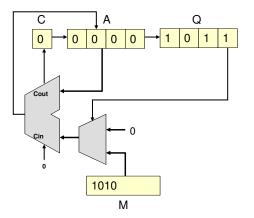

## Add and Shift Method

- Sequential algorithm

- n-bit \* n-bit multiply

- Adds 1 partial product per clock

- Shift running sum 1-bit right each clock

- Three *n*-bit Registers, 1 Adder

- At start:

- M = Multiplicand

- Q = Multiplier

- A = Answer => initialized to 0

- After completion

- A and Q concatenate to form 2n-bit answer

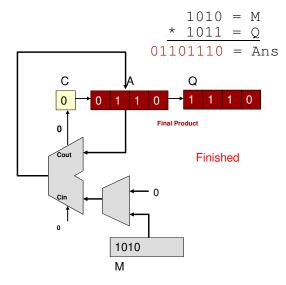

## Add and Shift Hardware

$$1010 = M$$

\*  $1011 = Q$

# Add and Shift Algorithm

- C=\_\_\_, A=\_\_\_\_

- Repeat the following \_\_\_\_\_\_

1010 \* 1011

# Add and Shift Multiplication

# Add and Shift Multiplication

### 1101 \* 0101 Example

# Sequential Multiplier Analysis

| • | Pros: |      |      |      |  |

|---|-------|------|------|------|--|

|   | _     |      |      |      |  |

|   |       | <br> | <br> | <br> |  |

• Cons:

\_\_\_\_\_

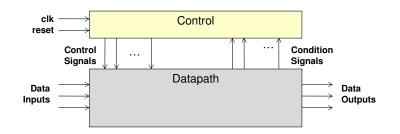

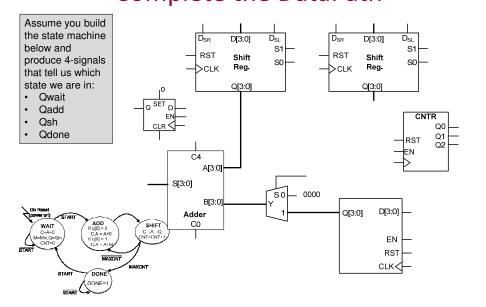

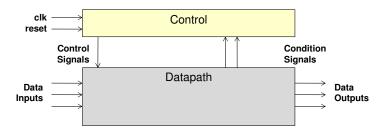

- · Control and Datapath Unit paradigm

- Separate logic into datapath elements that operate on data and control elements that generate control signals for datapath elements

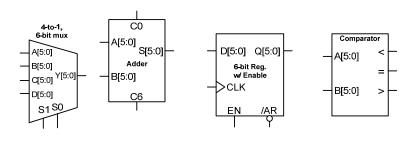

- Datapath: Adders, muxes, comparators, counters, registers (w/ enables)

- Control Unit: State machines/sequencers

# Let's Practice our Design Skills

- Break design into control and datapath

- This is the datapath

- 1 Adder

- 2-to-1 mux

- 2 shift registers (A/Q)

- 1 normal reg (M)

- 1 FF w/ Enable (C)

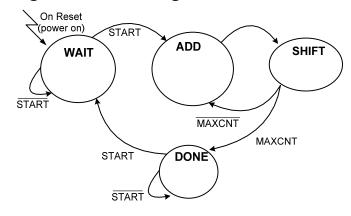

#### **State Machine Control**

From our high level datapath we can arrive at a high-level state diagram

### Refining our Design

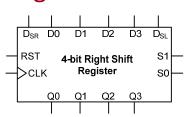

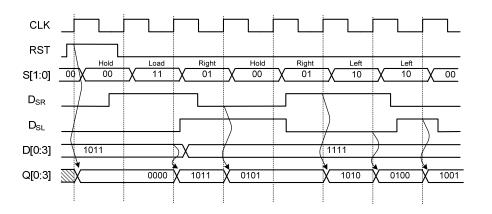

• But now we need to refine our design to actual components, specific control bits, etc.

- Shift registers come in many flavors, we'll just look at one example

- 4-bit Bi-directional Shift Register

- RST: synchronous reset

- S[1:0]: Hold, Right Shift, Left Shift, or Load

- DSL and DSR

- · Data to shift in from left or right

| CLK | ACLR | S1 | S0 | Q*[3:0]                 | (case) |

|-----|------|----|----|-------------------------|--------|

| 0,1 | Х    | Х  | Χ  | X Q[3:0]                |        |

| 1   | 1    | Х  | Χ  | 0000                    | Reset  |

| 1   | 0    | 0  | 0  | Q[3:0]                  | Hold   |

| 1   | 0    | 0  | 1  | D <sub>SR</sub> ,Q[3:1] | Right  |

| 1   | 0    | 1  | 0  | Q[2:0],D <sub>SL</sub>  | Left   |

| 1   | 0    | 1  | 1  | D[0:3]                  | Load   |

# **Shift Registers**

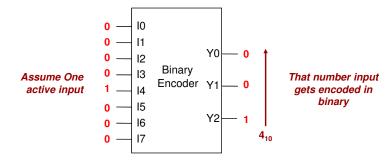

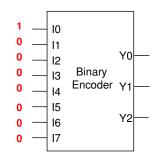

# Encoders

- Another common datapath component

- Opposite function of decoders

- Takes in 2<sup>n</sup> inputs and produces an n-bit number

#### **SIMPLE & PRIORITY ENCODERS**

### **Encoders**

What's inside an encoder?

| I <sub>0</sub> | I <sub>1</sub> | l <sub>2</sub> | l <sub>3</sub> | I <sub>4</sub> | I <sub>5</sub> | I <sub>6</sub> | I <sub>7</sub> | Y <sub>2</sub> | <b>Y</b> <sub>1</sub> | Y <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|----------------|

| 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              |                |                       |                |

| 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              |                |                       |                |

| 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0              |                |                       |                |

| 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              |                |                       |                |

| 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0              |                |                       |                |

| 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              |                |                       |                |

| 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              |                |                       |                |

| 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              |                |                       |                |

Deriving equations for  $Y_0$ ,  $Y_1$ ,  $Y_2$  is made simpler because of the assumption that only 1 input can be active at a time.

# USC Viterbi 2-3.46

#### **Encoders**

• What's inside an encoder?

| I <sub>0</sub> | I <sub>1</sub> | l <sub>2</sub> | l <sub>3</sub> | I <sub>4</sub> | I <sub>5</sub> | I <sub>6</sub> | <b>I</b> <sub>7</sub> | Y <sub>2</sub> | Υ <sub>1</sub> | Y <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|----------------|----------------|----------------|

| 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0                     | 0              | 0              | 0              |

| 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0                     | 0              | 0              | 1              |

| 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0                     | 0              | 1              | 0              |

| 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0                     | 0              | 1              | 1              |

| 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0                     | 1              | 0              | 0              |

| 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0                     | 1              | 0              | 1              |

| 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0                     | 1              | 1              | 0              |

| 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1                     | 1              | 1              | 1              |

|   | 10 |         |    |   |

|---|----|---------|----|---|

| _ | 11 |         |    |   |

|   | 12 |         | Y0 |   |

|   | 13 | Binary  |    |   |

|   | 14 | Encoder | Y1 | _ |

|   | 15 |         |    |   |

|   | 16 |         | Y2 |   |

| _ | 17 |         |    |   |

|   |    |         |    | l |

Y<sub>2</sub> = \_\_\_\_\_ Y<sub>1</sub> = \_\_\_\_\_ Y<sub>2</sub> =

### **Encoders**

A simple binary encoder can be made with just \_\_\_\_\_ gates

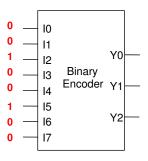

### **Problems**

- There is a problem...

- Our assumption is that only 1 input can be active at a time

- What happens if 2 or more inputs are active or if 0 inputs are active

## 2 or More Active Inputs

- What if I5 and I2 are active at the same time?

- Substitute values into equation

- Output will be '111' = 7

- Output is neither 2 nor 5, it's something different, 7

$Y_2 = 14 + 15 + 16 + 17$

$Y_1 = 12 + 13 + 16 + 17$

$Y_0 = 11 + 13 + 15 + 17$

# USC Viter bi 2-3.50

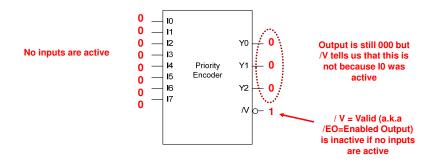

## **O Active Inputs**

- What if no inputs are active?

- Substitute values into equation

- Output will be

- Problem: '000' means that input 0 was active

- Can't \_\_\_\_\_ between when '000' means input 0 was active or no inputs was active

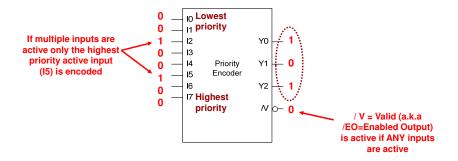

### **Priority Encoders**

- · Fix the 2 problems seen above

- Problem of more than 2 active inputs

- Assign priority to inputs and only encode the highest priority active input

- Problem of zero active inputs

- Create an extra output to indicate if any inputs are active

- We will call this output the "Valid" output (/V)

### **Priority Encoders**

- Fix the 2 problems seen above

- Problem of more than 2 active inputs

- Assign priority to inputs and only encode the highest priority active input

- · Problem of zero active inputs

- Create an extra output to indicate if any inputs are active

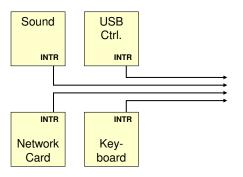

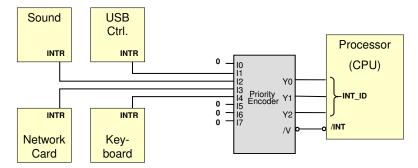

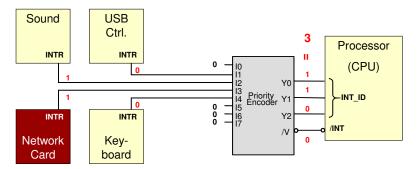

# **Encoder Application: Interrupts**

- I/O Devices in a computer need to request attention from the CPU...they need to "interrupt" the processor

- CPU cannot have a dedicated line to each I/O device (too many inputs and outputs) plus it can only service one device at a time

# **Encoder Application: Interrupts**

- Solution: Priority Encoder

- /INT input of CPU indicates SOME device is requesting attention

- INT\_ID inputs identify who is requesting attention

# **Encoder Application: Interrupts**

- Example: Sound and Network request interrupt at the same time

- · Network is highest priority and is encoded

- After network is handled, sound will cause interrupt

#### **VENDING MACHINE**

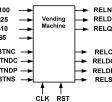

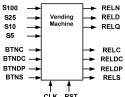

# **Vending Machine Controller**

- Consider a vending machine that sells Coke, Diet Coke, Sprite and Dr. Pepper

- Drinks cost \_

- Sensors indicate (for 1 clock cycle) when a user has entered a nickel, dime, quarter, or dollar bill

- Max. input amount is (beyond that the machine is not responsible for counting)

- Individual buttons for each drink allow the user to select their drink and if at least \$1 has been entered, a release signal for each drink should be asserted

- Making change will be considered in a future lab

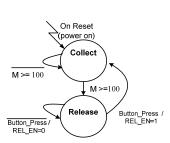

#### Money Collection & Release FSM

Consider the state machine and datapth only for money collection and release signal generation

## Digital System Design

- · Control and Datapath Unit paradigm

- Separate logic into datapath elements that operate on data and control elements that generate control signals for datapath elements

- Datapath: Adders, muxes, comparators, counters, registers (w/ enables)

- Control Unit: State machines/sequencers

#### Money Collection Datapath

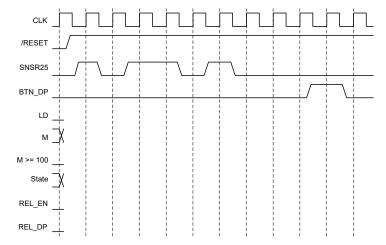

# Sample Operation Waveform