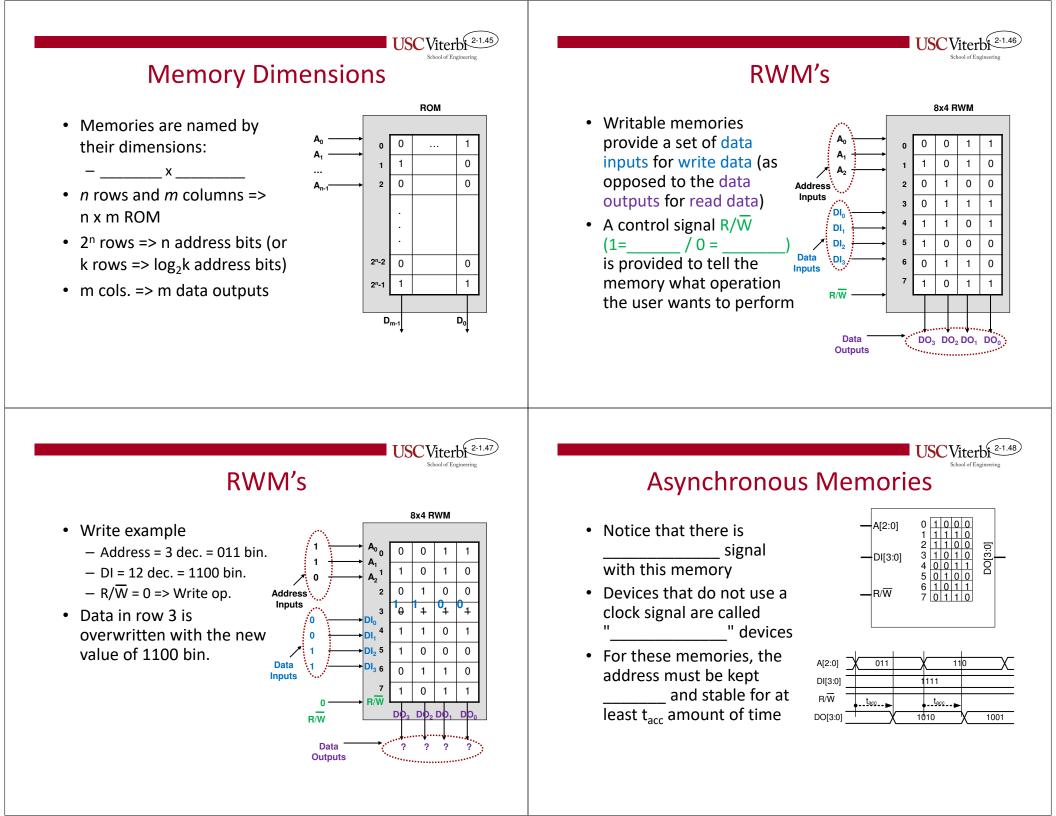

## Asynchronous vs. Synchronous Memories

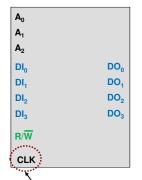

- Asynchronous memories use no CLK signal

- For read: Address and R/W signal must be held steady for a certain period of time before DO outputs become valid

- For write: Address, DI, and R/W signal must be held steady for a certain period of time before internal memory is updated

- Synchronous memories use a CLK signal

- For read: Address and R/W signal will be registered on the CLK edge and then DO will become valid during that subsequence clock cycle

- For write: Address, DI and R/W signals will be registered on the CLK edge and then the internal memory updated during the subsequent clock cycle

USC Viter bi 2-1.49

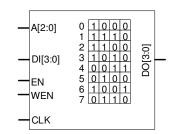

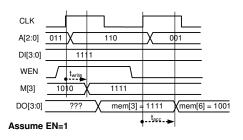

Synchronous memories add a clock signal and the input values at a clock edge will only be processed during the subsequence clock cycle

## Synchronous Timing

- For synchronous memories the address must be valid and stable at \_\_\_\_\_\_ but then may be changed

- EN = \_\_\_\_\_ enable (unless it is 1) the memory won't read or write

- WEN = \_\_\_\_

- -1 = Write / 0 = read

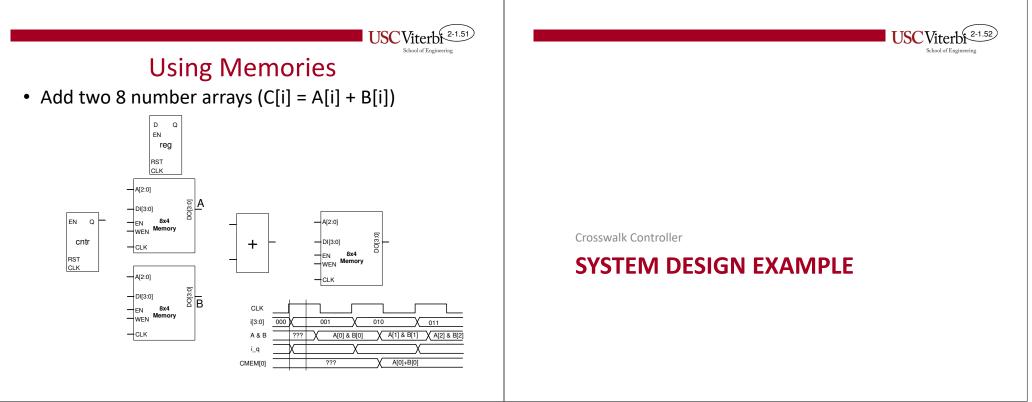

## School of Eng **Digital System Design Crosswalk Controller** Control and Datapath Unit paradigm • Design a crosswalk controller to ٠ adhere to the following description - Separate logic into datapath elements that operate on data and control elements that generate control signals for datapath elements • 8 ticks of the clock in the WALK phase - Datapath: Adders, muxes, comparators, counters, registers (w/ 8 ON/OFF BLINKING hand cycles (16 NUM(3:0 ٠ enables) total ticks) Control Unit: State machines/sequencers Count 8 downto 1 on the NUM display while hand is blinking NUM\_ON HAND WAI K clk Control • 16 cycles in the SOLID hand reset Control Condition . . . Signals Signals Datapath Data Data Outputs Inputs **USC**Viterbi **USC**Viter **Crosswalk State Machine Crosswalk Controller Operation** • Use a 4-bit counter to count cycles along with an additional gate or two... CLK Q(3:0) 0110 ΕN C7 WALK RESE1 BlinkOff CE WALK=1 NUM\_ON⊨1 P0 P1 P2 TC 00 Q1 4-bit 02 STATE CNTR 03 Р3 NUM ON ΡE тс RST BlinkOn HAND=1. NUM\_ON=1 NUM NOWALK CLK HAND=1

2-1.53

**USC**Viterbi

**USC** Viterb

## Summary

- You should now be able to build:

- Registers (w/ Enables)

- Counters

- Adders