**USC**Viter

# Spiral 1 / Unit 7

### State Machine Design

### Outcomes

- I know the difference between combinational and sequential logic and can name examples of each.

- I understand latency, throughput, and at least 1 technique to improve throughput

- I can identify when I need state vs. a purely combinational function

- I can convert a simple word problem to a logic function (TT or canonical form) or state diagram

- I can use Karnaugh maps to synthesize combinational functions with several outputs

- I understand how a register with an enable functions & is built

- I can design a working state machine given a state diagram

- I can implement small logic functions with complex CMOS gates

## STATE MACHINES OVERVIEW

|   | What is state?                                                                                                                                                                |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Decisions are generally influenced by not only what is happenin<br>, but based on the sum of experiences<br>- The sum of all previous experiences is what is known as state   |

| • | In a human, 'state' refers to the sum of everything that has<br>happened that has led you to where you are now and influence<br>your interpretation of your senses & thoughts |

| • | In a circuit, 'state' refers to all the bits being remembered ( or memory)                                                                                                    |

| • | In software, 'state' refers to all the values that are being used                                                                                                             |

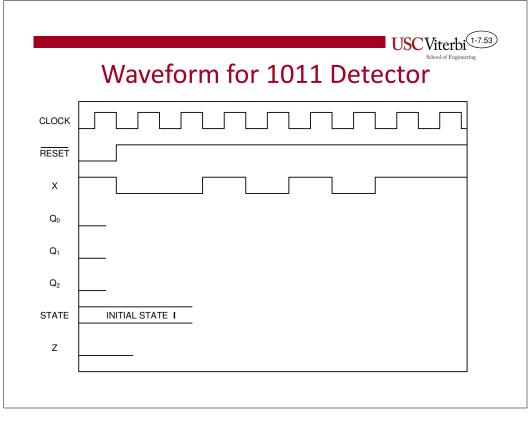

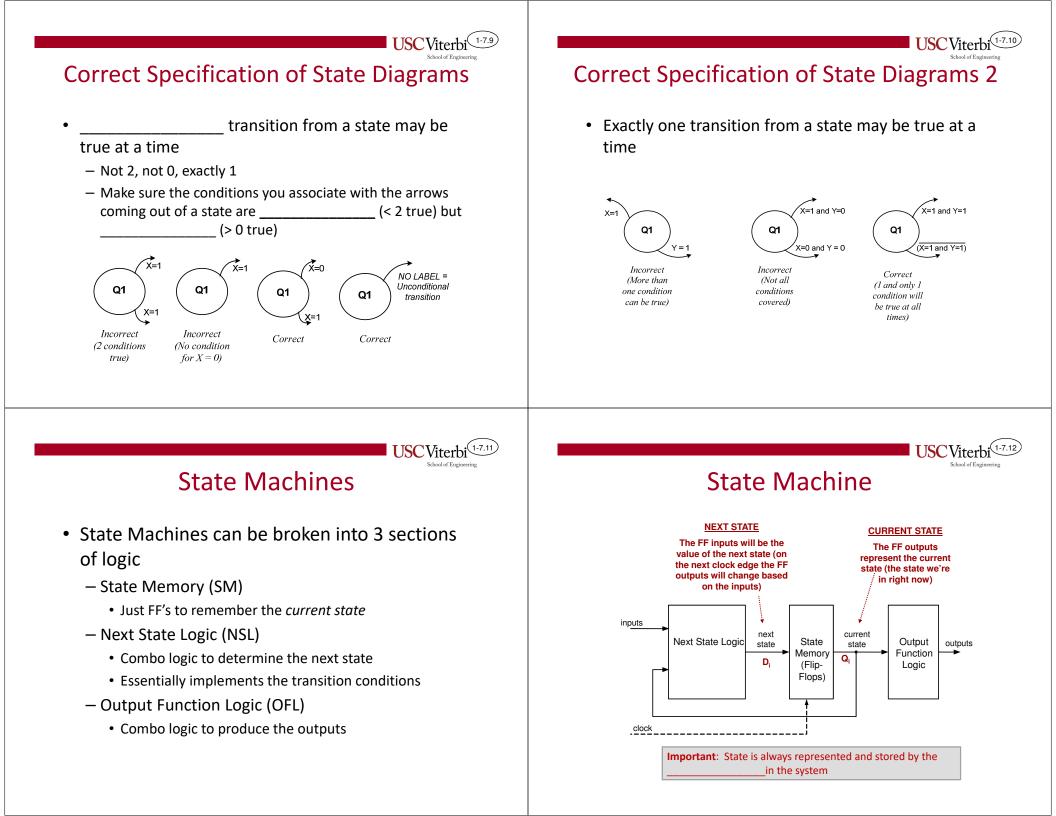

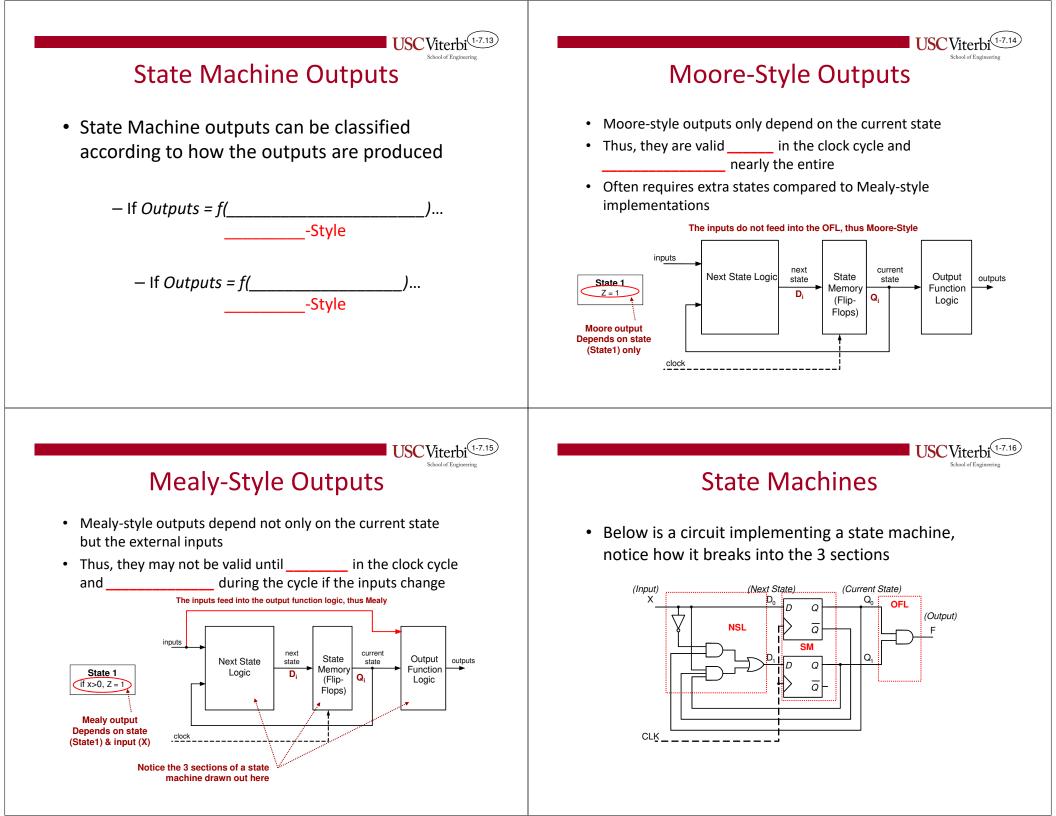

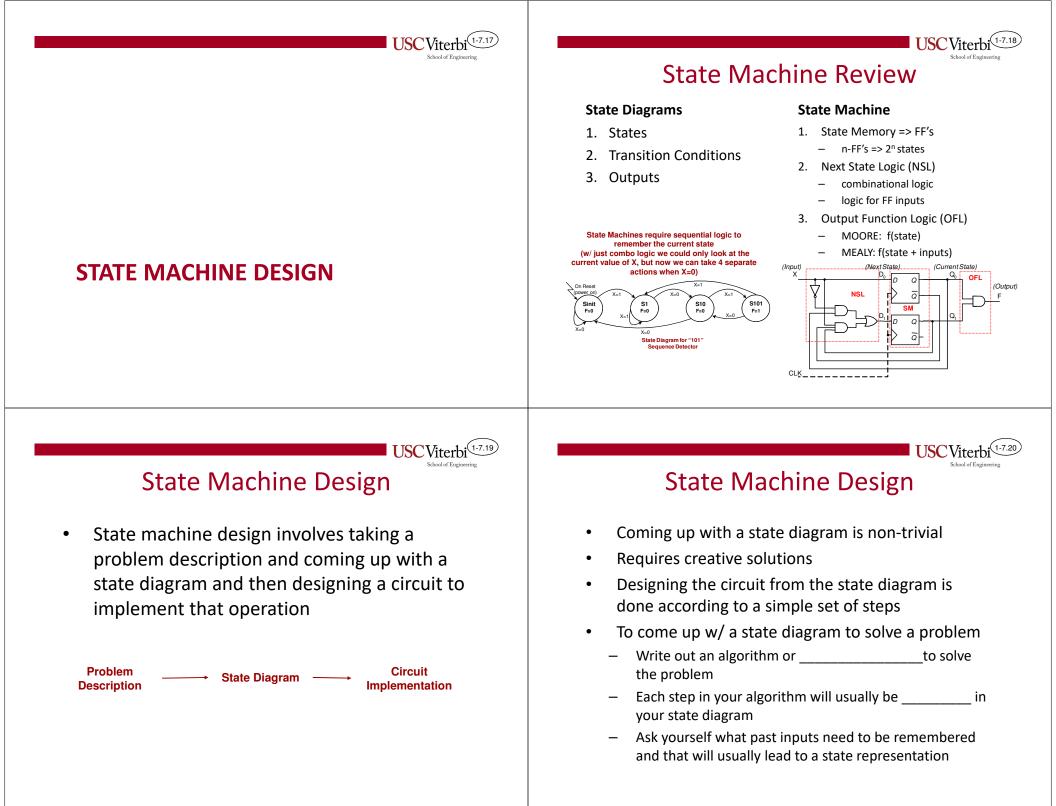

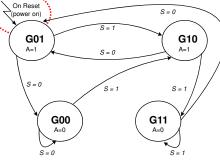

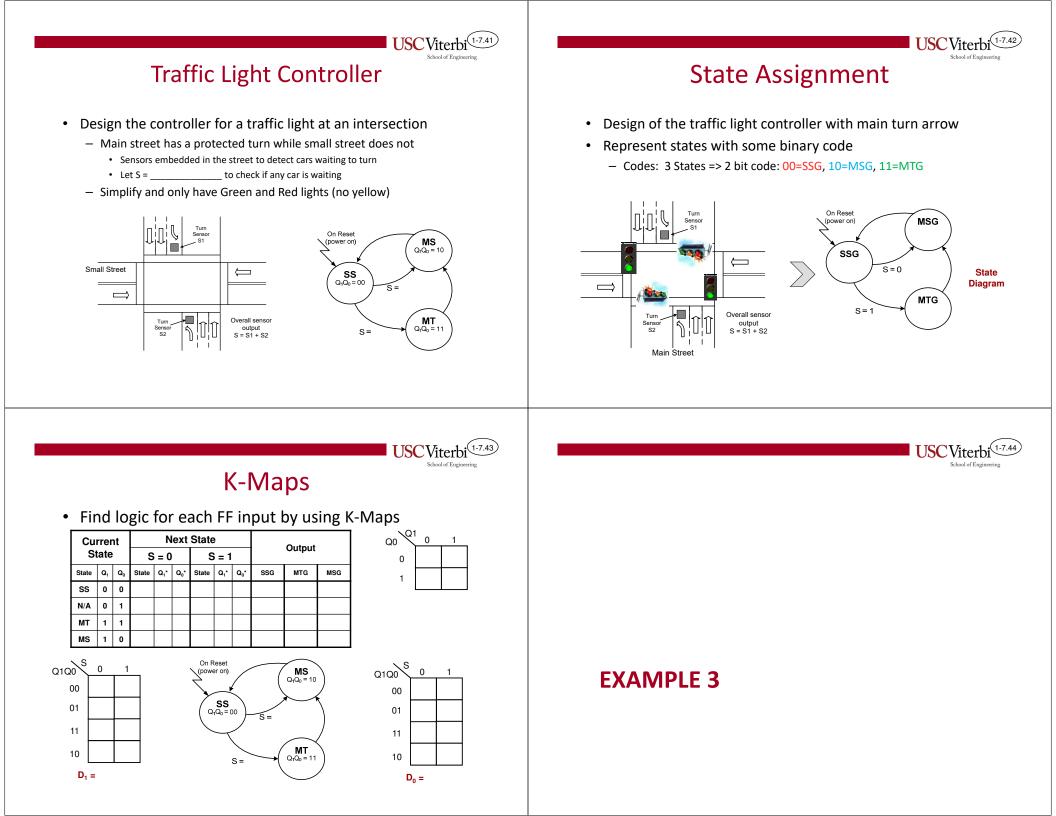

#### **USC**Viterbi State Machine Block Diagram State Machines A system that utilizes state is often referred to as a state machine (or finite state machine [FSM]) Provide the "brains" or control for electronic and electro-٠ mechanical systems Most state machines can be embodied in the following form ٠ Implement a set of steps (or algorithm) to control or solve a - Logic examines what's happening NOW (inputs) & from the PAST (state) to problem produce outputs and update the state (which will be used in the future to change the decision) Goal is to generate output values at • Inputs will go away or change, so state needs to Combine Sequential and Combinational logic elements summarize/capture anything that might be useful for the future Sequential Logic to remember what step (state) we're in · Encodes everything that has happened in the past Combinational Logic to produce outputs and find what state to go to Logic next Inputs Outputs · Generates outputs based on what state we're in and the input values (a.k.a. flowcharts) to specify the • Use operation of the corresponding state machine State (memory) **USC**Viterbi Another State Diagram Example State Machine Example Design a sequence detector to check for the combination "101" Sequence Detector should output F=1 when the ٠ "101" sequence 101 is found in consecutive order Input, X, provides 1-bit per clock ٠ Check the sequence of X for "101" in successive clocks If "101" detected, output Z=1 (Z=0 all other times) S101 Sinit S1 S10 F=0 F=0 F=0 F=1 "101" Х Sequence ⇒Ζ Detector CLK RESET State Diagram for "101" Sequence Detector

### 6 Steps of State Machine Design

- 1. State Diagram

- 2. Transition/Output Table

- 3. State Assignment

- Determine the # of FF's required

- Assign binary codes to replace symbolic names

- 4. Excitation Table (Rename Q\* to D)

- 5. K-Maps for NSL and OFL

- One K-Map for every FF input

- One K-Map for every output of OFL

- 6. Draw out the circuit

**USC**Viterb

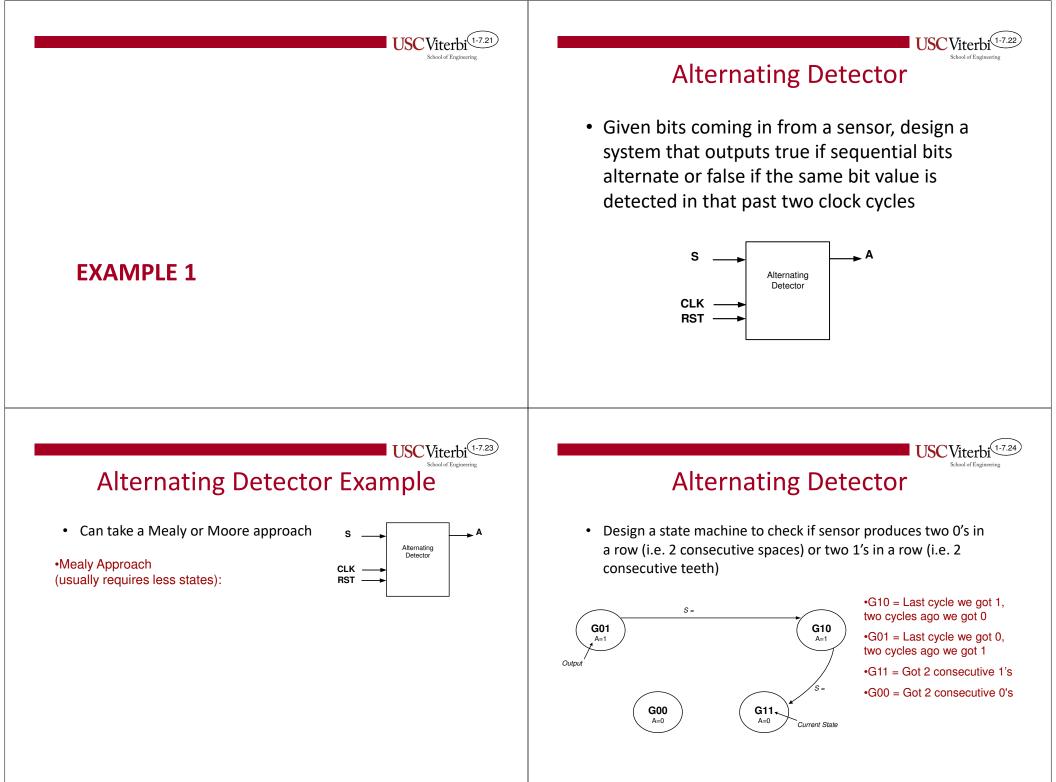

## **Transition Output Table**

Convert state diagram to transition/output table

Show Next State & Output as a function of Current State and Input

| Current<br>State | Input (S) | Next<br>State | Output<br>(A) |

|------------------|-----------|---------------|---------------|

| G01              | 0         |               | 1             |

| G01              | 1         |               | 1             |

| G11              | 0         |               | 0             |

| G11              | 1         |               | 0             |

| G00              | 0         |               | 0             |

| G00              | 1         |               | 0             |

| G10              | 0         |               | 1             |

| G10              | 1         |               | 1             |

USC Viterbi

**USC**Viterbi

# Transition Output Table

• Now assign binary codes to represent states

| ping                     | State | Q <sub>1</sub> | $Q_0$ |

|--------------------------|-------|----------------|-------|

| t Map                    | G01   | 0              | 0     |

| nen                      | G11   | 0              | 1     |

| Assign                   | G00   | 1              | 0     |

| State Assignment Mapping | G10   | 1              | 1     |

| S.                       |       |                |       |

| Curi<br>Sta |    | Input | Next | State | Output |

|-------------|----|-------|------|-------|--------|

| Q1          | Q0 | S     | Q1*  | Q0*   | А      |

| 0           | 0  | 0     | 1    | 0     | 1      |

| 0           | 0  | 1     | 1    | 1     | 1      |

| 0           | 1  | 0     | 0    | 0     | 0      |

| 0           | 1  | 1     | 0    | 1     | 0      |

| 1           | 0  | 0     | 1    | 0     | 0      |

| 1           | 0  | 1     | 1    | 1     | 0      |

| 1           | 1  | 0     | 0    | 0     | 1      |

| 1           | 1  | 1     | 0    | 1     | 1      |

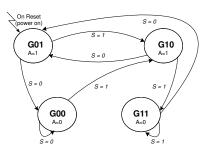

# **Transition Output Table**

### • Convert state diagram to transition/output table

| Curre | nt Stat        | ā     |       |       | Next S | tate  |        | Output |

|-------|----------------|-------|-------|-------|--------|-------|--------|--------|

| Ourie |                |       | S     | 6 = 0 |        | S     | Output |        |

| State | Q <sub>1</sub> | $Q_0$ | State |       |        | State |        | А      |

| G01   | 0              | 0     | G00   |       |        | G10   |        | 1      |

| G11   | 0              | 1     | G01   |       |        | G11   |        | 0      |

| G10   | 1              | 1     | G01   |       |        | G11   |        | 1      |

| G00   | 1              | 0     | G00   |       |        | G10   |        | 0      |

|       |                |                | 5     | 0 = 0          |                | 5     | = 1            |                |   |

|-------|----------------|----------------|-------|----------------|----------------|-------|----------------|----------------|---|

| State | Q <sub>1</sub> | Q <sub>0</sub> | State | D <sub>1</sub> | D <sub>0</sub> | State | D <sub>1</sub> | D <sub>0</sub> | А |

| G01   | 0              | 0              | G00   | 1              | 0              | G10   | 1              | 1              | 1 |

| G11   | 0              | 1              | G01   | 0              | 0              | G11   | 0              | 1              | 0 |

| G10   | 1              | 1              | G01   | 0              | 0              | G11   | 0              | 1              | 1 |

| G00   | 1              | 0              | G00   | 1              | 0              | G10   | 1              | 1              | 0 |

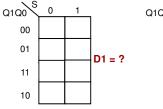

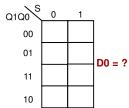

Q1Q0

G10

G00

G01

G00

G11

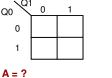

| Q0 Q1 | 0 | 1 |  |

|-------|---|---|--|

| 0     | 1 | 0 |  |

| 1     | 0 | 1 |  |

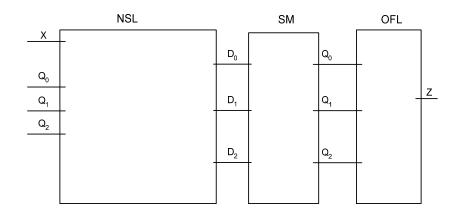

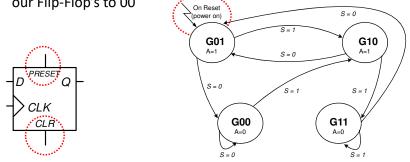

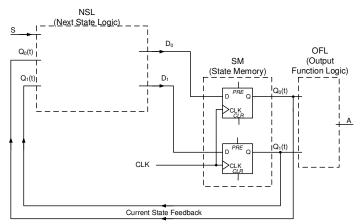

#### **USC**Viterb **USC**Viterbi Implementing the Circuit Implementing an Initial State • How can we make the machine start in G0 on reset Implements the alternating detector (or power on?) OFL (Output NSL SM • Flip-flops by themselves will initalize to a random Function Logic) (Next State Logic) (State Memory) state (1 or 0) when power is turned on $D_0$

USC Viter bi

# Implementing an Initial State

D₁

Current State Feedback

unused

Q₁(t

$Q_0(t)$

>clk

CLK

CLK

- Use the CLEAR and PRESET inputs on our flip-flops in the state memory

- When CLEAR is active the FF initializes Q=0

- When PRESET is active the FF initializes Q=1

- We assigned G0 the binary code  $Q_1Q_0=00$  so we must initialize our Flip-Flop's to 00

# Implementing an Initial State

**USC**Viterb

• Use the CLR inputs of your FF's along with the RESET signal to initialize them to 0's and tie off the PRE inputs

#### USC Viter bi School of Engir Implementing an Initial State Alternate State Assignment • Important Fact: The \_\_\_\_\_ we assign to our states can have a • When RESET is activated Q's initialize to 0 and then big impact on the size of the NSL and OFL when it goes back to 1 the Q's look at the D inputs • Let us work again with a different set of assignments Forces Q's to 0 because it's Next State connected to the CLR inputs Current State S = 0 $Q_1 \mid Q_0$ State Q<sub>1</sub> Q<sub>0</sub> State State State RESET 0 0 G01 G01 0 0 G00 G10 Once RESET goes to 0, the FF's G11 0 1 look at the D inputs Q0 \_\_\_\_\_

**USC**Viterbi

## Alternate State Assignment

| Curre | nt Stat        | ٥              |       |            | Next S     | tate  |            |            | Output |

|-------|----------------|----------------|-------|------------|------------|-------|------------|------------|--------|

| Ouric | ni Olui        | 0              | S     | 6 = 0      |            | S     |            | Output     |        |

| State | Q <sub>1</sub> | Q <sub>0</sub> | State | Q1*=<br>D1 | Q0*=<br>D0 | State | Q1*<br>=D1 | Q0*<br>=D0 | А      |

| G01   | 0              | 0              | G00   | 1          | 1          | G10   | 0          | 1          | 1      |

| G10   | 0              | 1              | G01   | 0          | 0          | G11   | 1          | 0          | 1      |

| G00   | 1              | 1              | G00   | 1          | 1          | G10   | 0          | 1          | 0      |

| G11   | 1              | 0              | G01   | 0          | 0          | G11   | 1          | 0          | 0      |

Q1

Q0

### **EXAMPLE 2**

G10

G00

G11

G10

G00

1 1

1 0

**Old Assignments**

0

1 1

1 New Assignments

1

0

G01

G00

G01

USC Viter bi

Out

put

А

1

1

0

0

S = 1

G11

G10

G11

USCViterbi School of Engineering

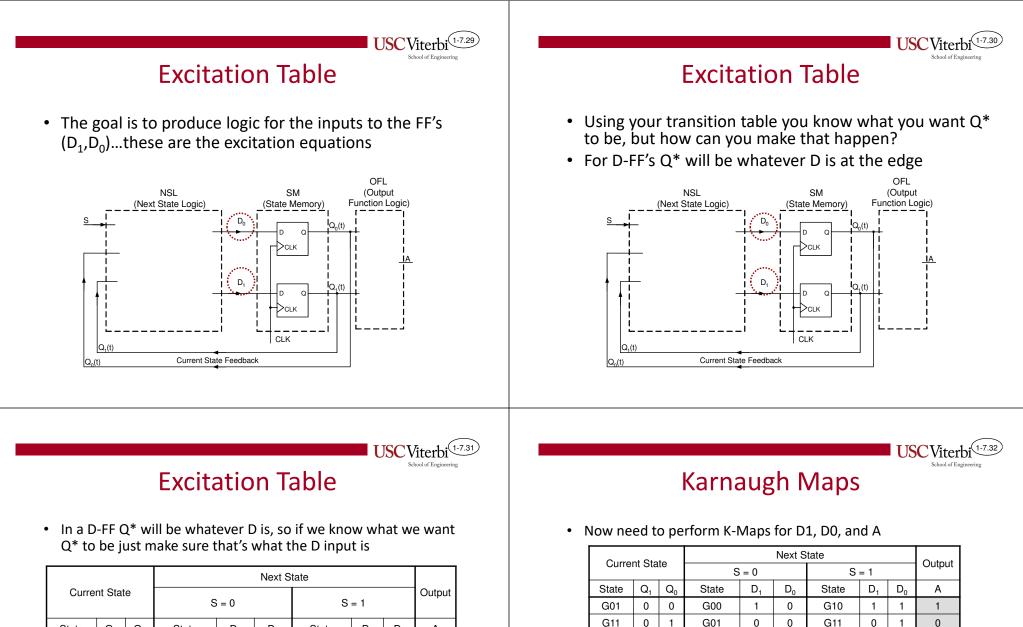

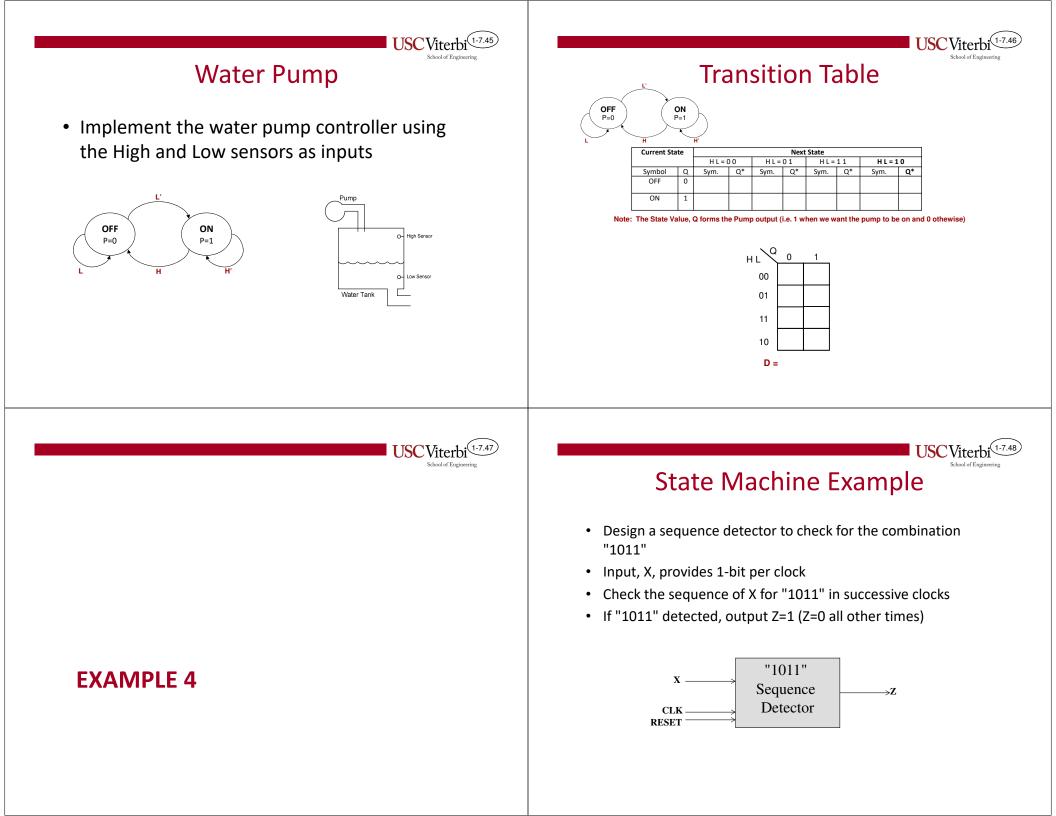

## State Diagram

• Be sure to handle overlapping sequences

Sinit Z=0 • Translate the state diagram into the transition output table

|       | urren | + State |    |        |     |     | Next | State  |     |     |     | Outp |

|-------|-------|---------|----|--------|-----|-----|------|--------|-----|-----|-----|------|

|       | unen  | l State |    |        | X = | 0   |      |        | X = | 1   |     | ut   |

| State | Q2    | Q1      | Q0 | State* | Q2* | Q1* | Q0*  | State* | Q2* | Q1* | Q0* | Z    |

| Sinit | 0     | 0       | 0  |        |     |     |      |        |     |     |     | 0    |

| S10   | 0     | 0       | 1  |        |     |     |      |        |     |     |     | 0    |

| S1    | 0     | 1       | 1  |        |     |     |      |        |     |     |     | 0    |

| S101  | 0     | 1       | 0  |        |     |     |      |        |     |     |     | 0    |

| S1011 | 1     | 1       | 0  |        |     |     |      |        |     |     |     | 1    |

USC Viterbi

Q1Q0<sup>2</sup>

00

01 0 d

0 1 0 d

11 0

10 0

Z = Q2

# NSL & OFL

| ~     |       |        | _  |        | Next State  |    |    |        |    |     |    |     |  |

|-------|-------|--------|----|--------|-------------|----|----|--------|----|-----|----|-----|--|

| C     | urren | t Stat | e  |        | X = 0 X = 1 |    |    |        |    | : 1 |    | put |  |

| State | Q2    | Q1     | Q0 | State* | D2          | D1 | D0 | State* | D2 | D1  | D0 | Z   |  |

| Sinit | 0     | 0      | 0  | Sinit  | 0           | 0  | 0  | S1     | 0  | 1   | 1  | 0   |  |

| S10   | 0     | 0      | 1  | Sinit  | 0           | 0  | 0  | S101   | 0  | 1   | 0  | 0   |  |

| S1    | 0     | 1      | 1  | S10    | 0           | 0  | 1  | S1     | 0  | 1   | 1  | 0   |  |

| S101  | 0     | 1      | 0  | S10    | 0           | 0  | 1  | S1011  | 1  | 1   | 0  | 0   |  |

| S1011 | 1     | 1      | 0  | S10    | 0           | 0  | 1  | S1     | 0  | 1   | 1  | 1   |  |

Q1Q0 00 Q1Q0 00 Q1Q0 00 01 11 10 01 11 10 01 11 10 0 d d 0 0 d d 1 d d 1 00 00 0 00 01 0 d d 0 01 0 d 01 d 0 d d 0 0 d 0 0 d 11 d 11 d d 11 [[1 d 0 0 0 1 0 0 10 10 10  $D_1 = X$  $D_0 = Q2 + Q1Q0 + X'Q1 + XQ1'Q0'$ D<sub>2</sub> = X•Q2'•Q1•Q0'

# Drawing the Circuit

**USC**Viterbi