# Spiral 1 / Unit 7

State Machine Design

## Outcomes

School of Engineering

- I know the difference between combinational and sequential logic and can name examples of each.

- I understand latency, throughput, and at least 1 technique to improve throughput

- I can identify when I need state vs. a purely combinational function

- I can convert a simple word problem to a logic function (TT or canonical form) or state diagram

- I can use Karnaugh maps to synthesize combinational functions with several outputs

- I understand how a register with an enable functions & is built

- I can design a working state machine given a state diagram

- I can implement small logic functions with complex CMOS gates

#### **STATE MACHINES OVERVIEW**

## What is state?

- Decisions are generally influenced by not only what is happening NOW, but based on the sum of PREVIOUS experiences

- The sum of all previous experiences is what is known as state

- In a human, 'state' refers to the sum of everything that has happened that has led you to where you are now and influences your interpretation of your senses & thoughts

- In a circuit, 'state' refers to all the bits being remembered (registers or memory)

- In software, 'state' refers to all the variable values that are being used

## State Machine Block Diagram

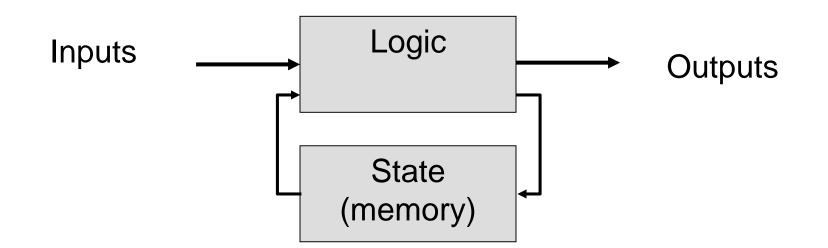

- A system that utilizes state is often referred to as a state machine (or finite state machine [FSM])

- Most state machines can be embodied in the following form

- Logic examines what's happening NOW (inputs) & from the PAST (state) to produce outputs and update the state (which will be used in the future to change the decision)

- Inputs will go away or change, so state needs to summarize/capture anything that might be useful for the future

## **State Machines**

- Provide the "brains" or control for electronic and electromechanical systems

- Implement a set of steps (or algorithm) to control or solve a problem

- Goal is to generate output values at specific times

- Combine Sequential and Combinational logic elements

- Sequential Logic to remember what step (state) we're in

- Encodes everything that has happened in the past

- Combinational Logic to produce outputs and find what state to go to next

- Generates outputs based on what state we're in and the input values

- Use state diagrams (a.k.a. flowcharts) to specify the operation of the corresponding state machine

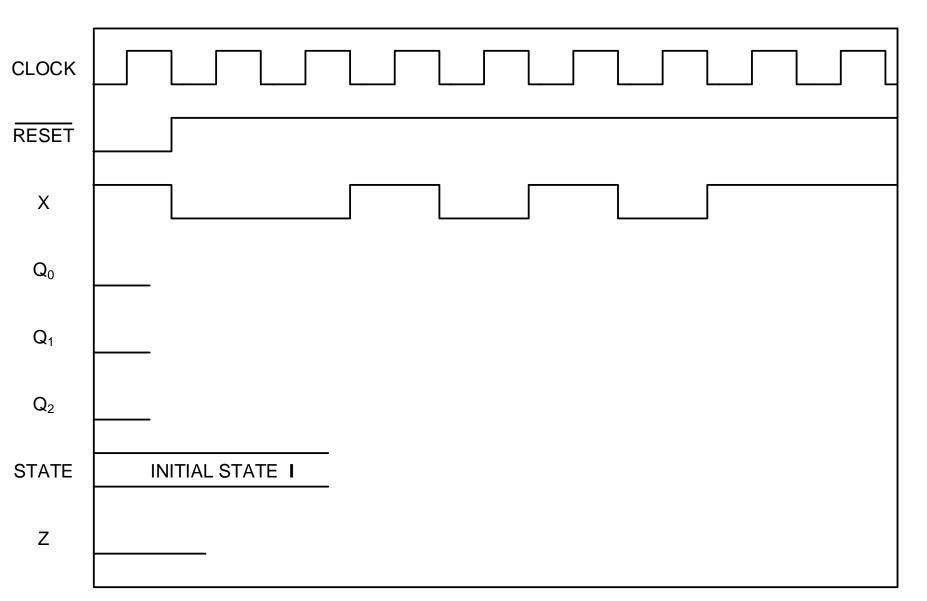

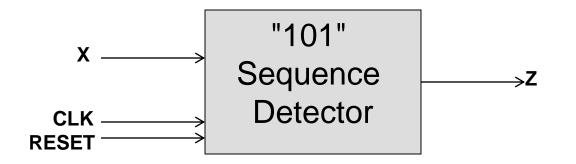

## State Machine Example

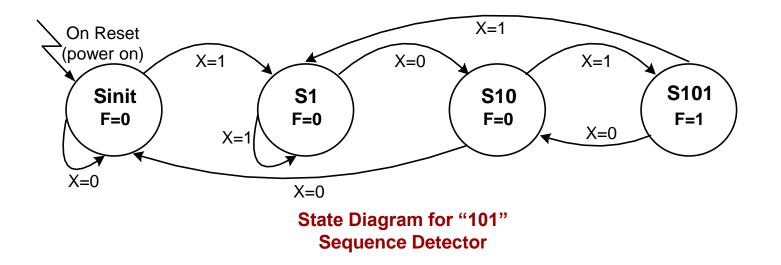

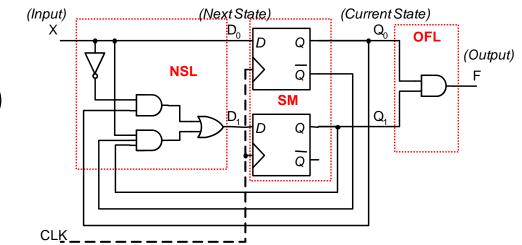

- Design a sequence detector to check for the combination "101"

- Input, X, provides 1-bit per clock

- Check the sequence of X for "101" in successive clocks

- If "101" detected, output Z=1 (Z=0 all other times)

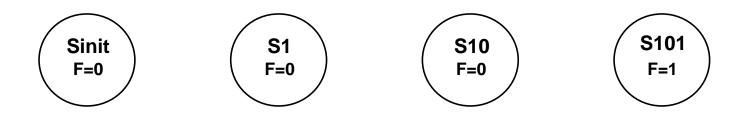

• "101" Sequence Detector should output F=1 when the sequence 101 is found in consecutive order

State Diagram for "101" Sequence Detector

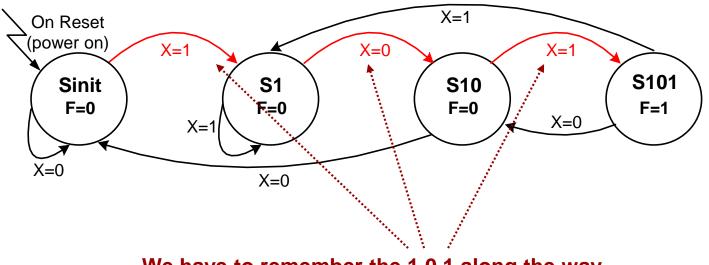

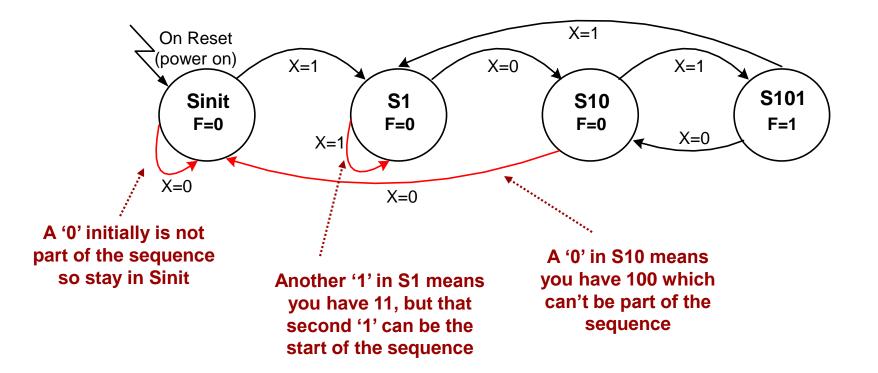

• "101" Sequence Detector should output F=1 when the sequence 101 is found in consecutive order

• "101" Sequence Detector should output F=1 when the sequence 101 is found in consecutive order

We have to remember the 1,0,1 along the way

• "101" Sequence Detector should output F=1 when the sequence 101 is found in consecutive order

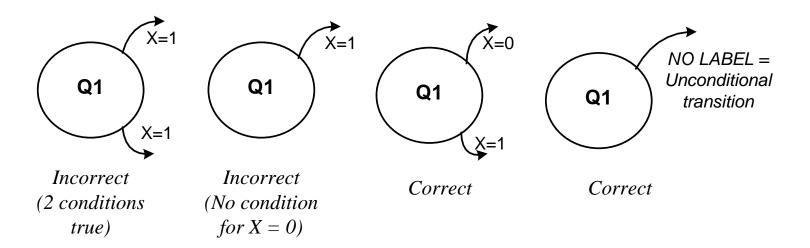

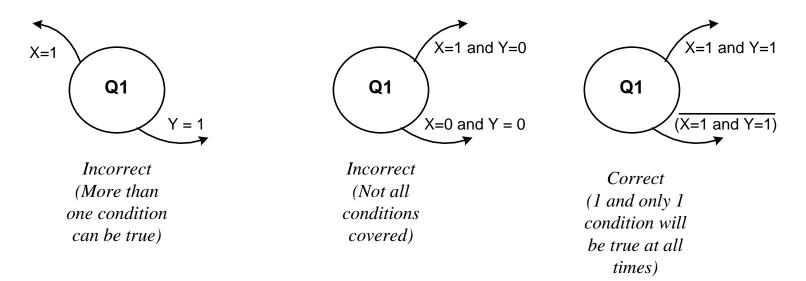

#### **Correct Specification of State Diagrams**

- Exactly one transition from a state may be true at a time

- Not 2, not 0, exactly 1

- Make sure the conditions you associate with the arrows coming out of a state are **mutually exclusive** (< 2 true) but **all inclusive** (> 0 true)

#### **Correct Specification of State Diagrams 2**

- Exactly one transition from a state may be true at a time

- Not 2, not 0, exactly 1

- Make sure the conditions you associate with the arrows coming out of a state are **mutually exclusive** (< 2 true) but all inclusive (> 0 true)

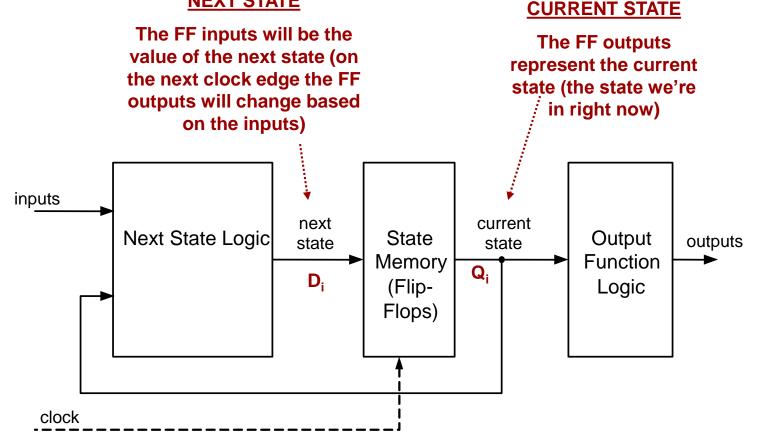

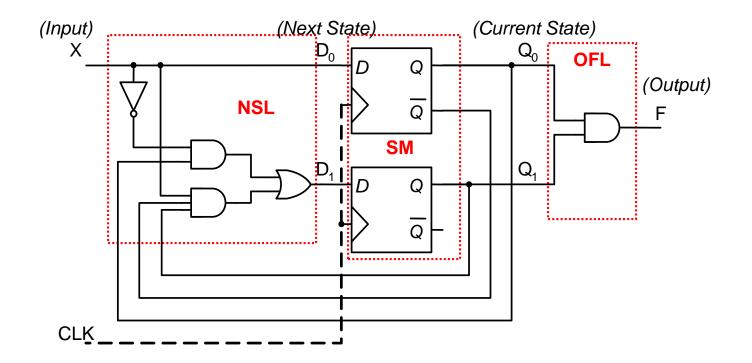

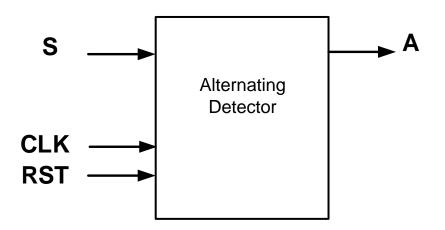

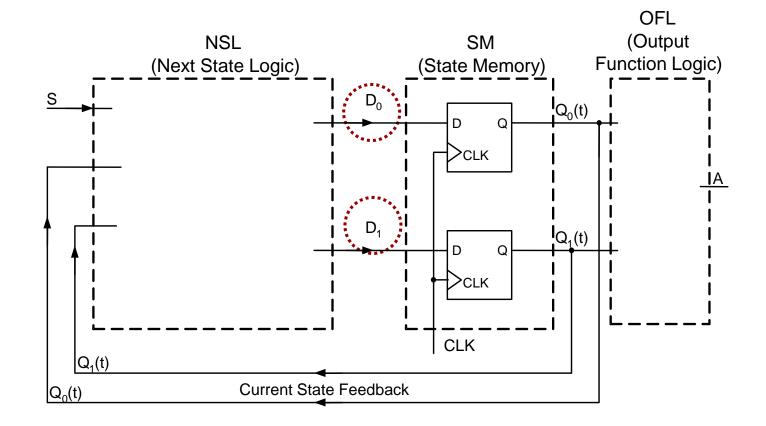

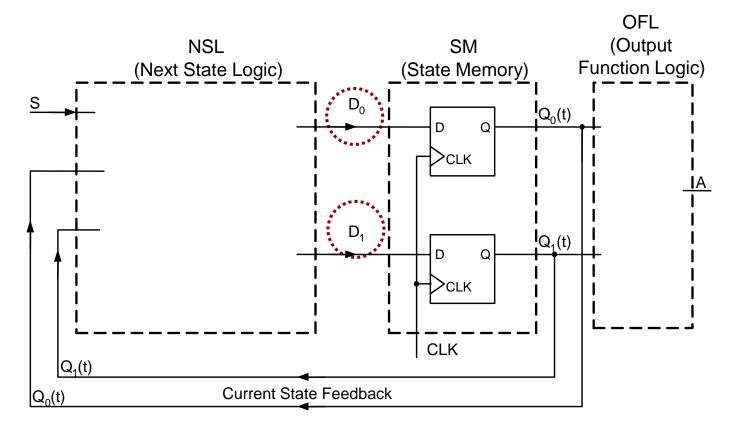

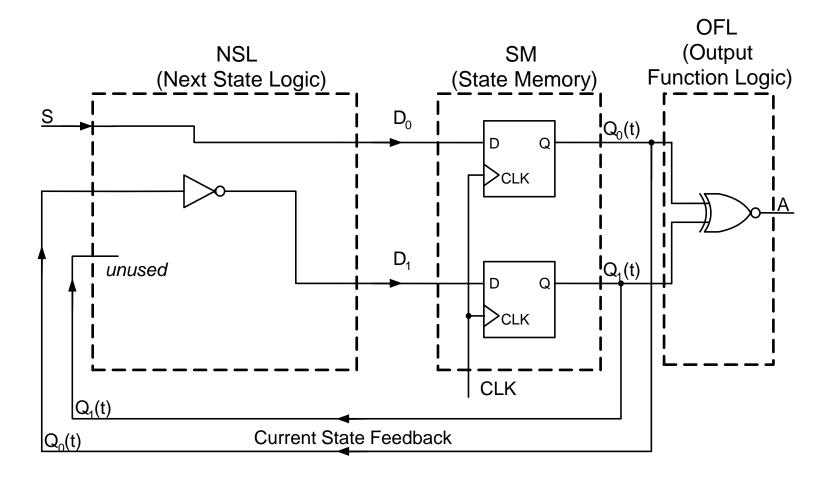

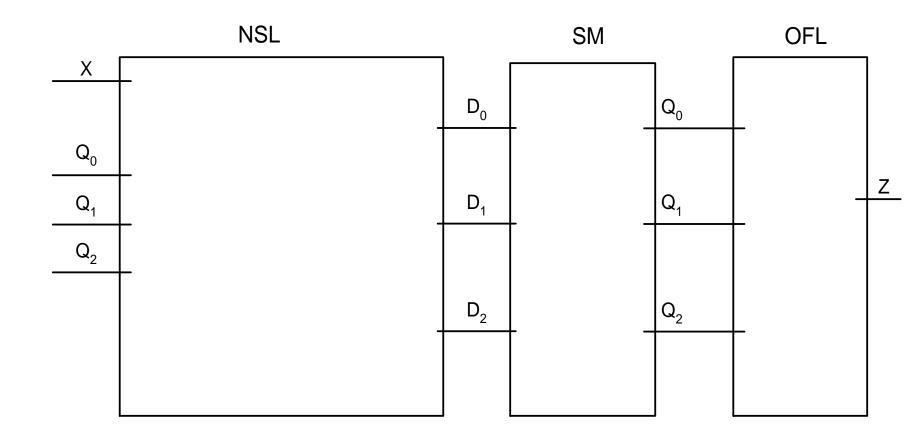

## **State Machines**

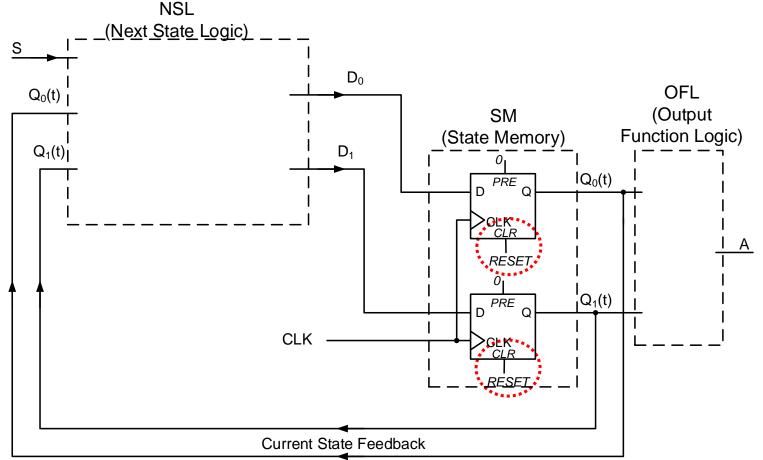

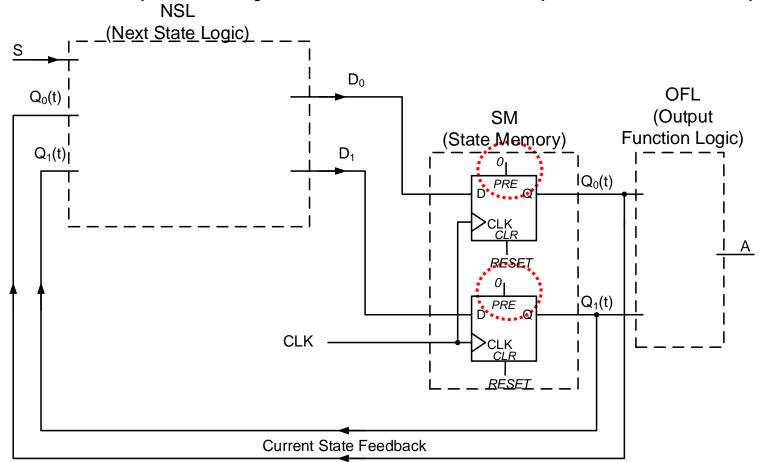

- State Machines can be broken into 3 sections of logic

- State Memory (SM)

- Just FF's to remember the *current state*

- Next State Logic (NSL)

- Combo logic to determine the next state

- Essentially implements the transition conditions

- Output Function Logic (OFL)

- Combo logic to produce the outputs

#### State Machine

1-7.15

School of Engineering

#### **NEXT STATE**

**Important**: State is always represented and stored by the flip-flop outputs in the system

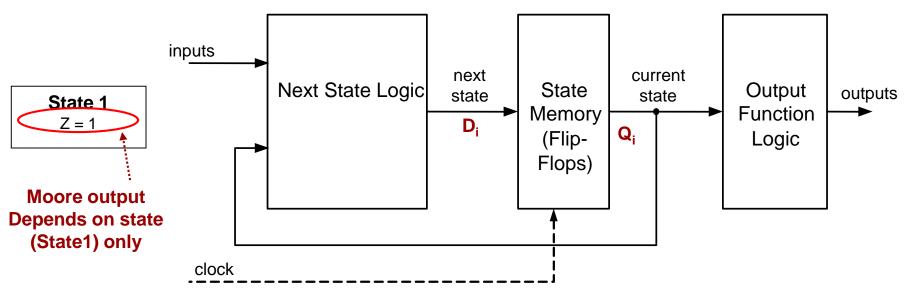

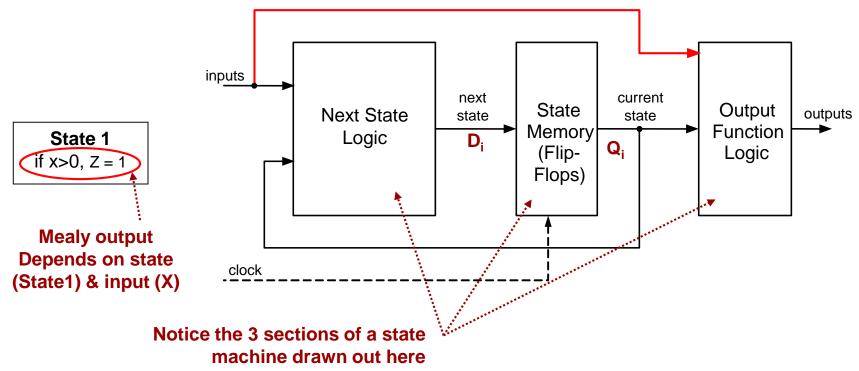

## **State Machine Outputs**

• State Machine outputs can be classified according to how the outputs are produced

– If Outputs = f(current state, external inputs)...

MEALY-Style

– If Outputs = f(current state)...

MOORE-Style

## Moore-Style Outputs

- Moore-style outputs only depend on the current state

- Thus, they are valid *early* in the clock cycle and *stay steady/valid* nearly the entire

- Often requires extra states compared to Mealy-style implementations

#### The inputs do not feed into the OFL, thus Moore-Style

# Mealy-Style Outputs

- Mealy-style outputs depend not only on the current state but the external inputs

- Thus, they may not be valid until *late* in the clock cycle and *may change* during the cycle if the inputs change

The inputs feed into the output function logic, thus Mealy

#### **State Machines**

• Below is a circuit implementing a state machine, notice how it breaks into the 3 sections

## **STATE MACHINE DESIGN**

## State Machine Review

#### **State Diagrams**

- 1. States

- 2. Transition Conditions

- 3. Outputs

#### **State Machine**

- 1. State Memory => FF's

- n-FF's => 2<sup>n</sup> states

1-7.21

School of Engineering

- 2. Next State Logic (NSL)

- combinational logic

- logic for FF inputs

- 3. Output Function Logic (OFL)

- MOORE: f(state)

- MEALY: f(state + inputs)

State Machines require sequential logic to remember the current state (w/ just combo logic we could only look at the current value of X, but now we can take 4 separate actions when X=0)

## State Machine Design

State machine design involves taking a problem description and coming up with a state diagram and then designing a circuit to implement that operation

## State Machine Design

- Coming up with a state diagram is non-trivial

- Requires creative solutions

- Designing the circuit from the state diagram is done according to a simple set of steps

- To come up w/ a state diagram to solve a problem

- Write out an algorithm or series of steps to solve the problem

- Each step in your algorithm will usually be one state in your state diagram

- Ask yourself what past inputs need to be remembered and that will usually lead to a state representation

#### **EXAMPLE 1**

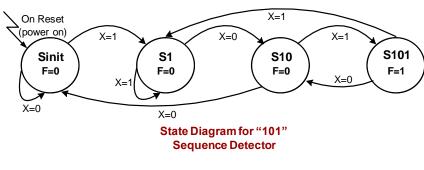

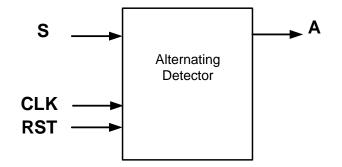

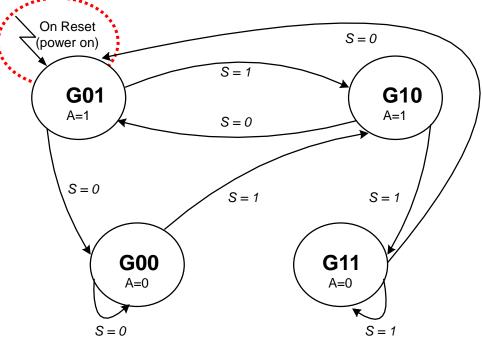

## **Alternating Detector**

Given bits coming in from a sensor, design a system that outputs true if sequential bits alternate or false if the same bit value is detected in that past two clock cycles

# Alternating Detector Example

• Can take a Mealy or Moore approach

•Mealy Approach (usually requires less states):

-7.26

School of Engineering

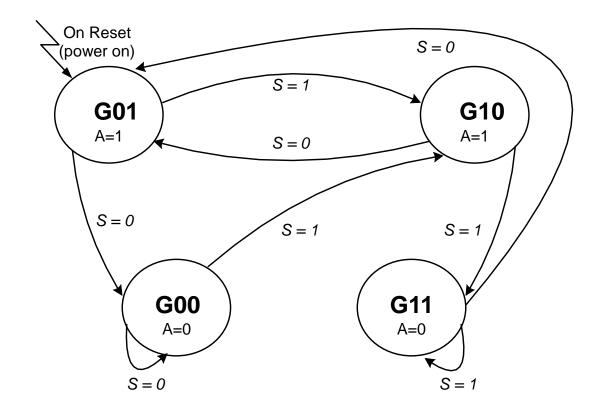

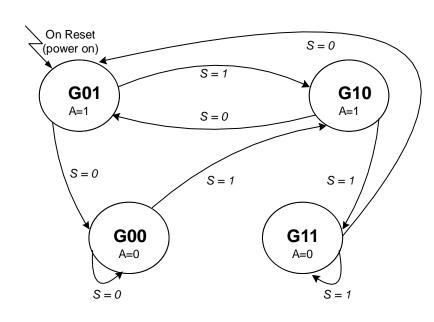

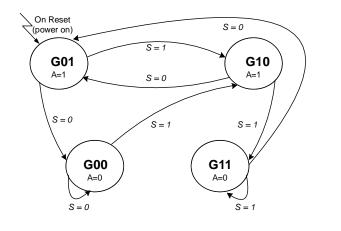

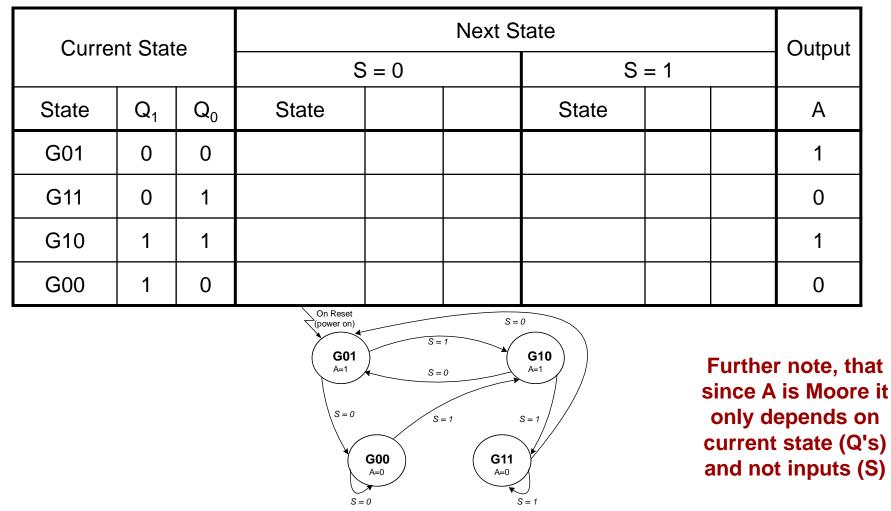

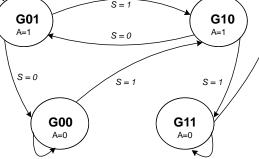

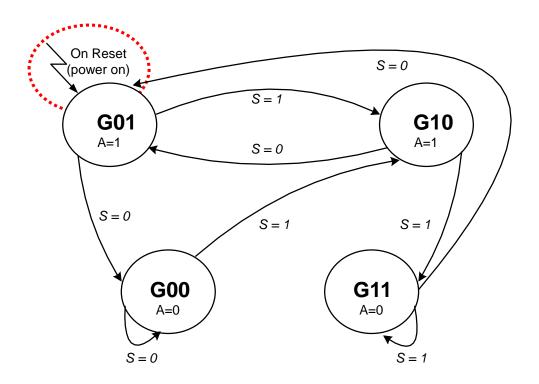

## **Alternating Detector**

Design a state machine to check if sensor produces two 0's in a row (i.e. 2 consecutive spaces) or two 1's in a row (i.e. 2 consecutive teeth)

•G10 = Last cycle we got 1, two cycles ago we got 0

1-7.27

School of Engineering

•G01 = Last cycle we got 0, two cycles ago we got 1

•G11 = Got 2 consecutive 1's

•G00 = Got 2 consecutive 0's

### 6 Steps of State Machine Design

- 1. State Diagram

- 2. Transition/Output Table

- 3. State Assignment

- Determine the # of FF's required

- Assign binary codes to replace symbolic names

- 4. Excitation Table (Rename Q\* to D)

- 5. K-Maps for NSL and OFL

- One K-Map for every FF input

- One K-Map for every output of OFL

- 6. Draw out the circuit

## **Transition Output Table**

- Convert state diagram to transition/output table

- Show Next State & Output as a function of Current State and Input

| Current<br>State | Input (S) | Next<br>State | Output<br>(A) |

|------------------|-----------|---------------|---------------|

| G01              | 0         | G00           | 1             |

| G01              | 1         | G10           | 1             |

| G11              | 0         | G01           | 0             |

| G11              | 1         | G11           | 0             |

| G00              | 0         | G00           | 0             |

| G00              | 1         | G10           | 0             |

| G10              | 0         | G01           | 1             |

| G10              | 1         | G11           | 1             |

## **Transition Output Table**

• Now assign binary codes to represent states

| ping                     | State | Q <sub>1</sub> | Q <sub>0</sub> |

|--------------------------|-------|----------------|----------------|

| t Map                    | G01   | 0              | 0              |

| nmen                     | G11   | 0              | 1              |

| Assign                   | G00   | 1              | 0              |

| State Assignment Mapping | G10   | 1              | 1              |

| Current<br>State |    | Input | Next | State | Output |  |

|------------------|----|-------|------|-------|--------|--|

| Q1               | Q0 | S     | Q1*  | Q0*   | А      |  |

| 0                | 0  | 0     | 1    | 0     | 1      |  |

| 0                | 0  | 1     | 1    | 1     | 1      |  |

| 0                | 1  | 0     | 0    | 0     | 0      |  |

| 0                | 1  | 1     | 0    | 1     | 0      |  |

| 1                | 0  | 0     | 1    | 0     | 0      |  |

| 1                | 0  | 1     | 1    | 1     | 0      |  |

| 1                | 1  | 0     | 0    | 0     | 1      |  |

| 1                | 1  | 1     | 0    | 1     | 1      |  |

## **Transition Output Table**

• Might be easier to visualize truth table with current state down vertical axis and input along horizontal axis

#### **Transition Output Table**

• Convert state diagram to transition/output table

| Current State                                                     |                |       | Next State |  |  |       |        |  | Output |

|-------------------------------------------------------------------|----------------|-------|------------|--|--|-------|--------|--|--------|

|                                                                   |                |       | S = 0      |  |  | S     | Output |  |        |

| State                                                             | Q <sub>1</sub> | $Q_0$ | State      |  |  | State |        |  | А      |

| G01                                                               | 0              | 0     | G00        |  |  | G10   |        |  | 1      |

| G11                                                               | 0              | 1     | G01        |  |  | G11   |        |  | 0      |

| G10                                                               | 1              | 1     | G01        |  |  | G11   |        |  | 1      |

| G00                                                               | 1              | 0     | G00        |  |  | G10   |        |  | 0      |

| On Reset<br>(power on) $S = 0$<br><b>G01</b><br>A=1 $S = 0G10A=1$ |                |       |            |  |  |       |        |  |        |

S = 1

S = 0

#### State Assignment

• Replace Next state names with desired next state combination

|       |                |                | Next State |                  |                  |       |                  |                  |   |

|-------|----------------|----------------|------------|------------------|------------------|-------|------------------|------------------|---|

| Curre | nt Stat        | е              | S = 0      |                  |                  | S     | Output           |                  |   |

| State | Q <sub>1</sub> | Q <sub>0</sub> | State      | Q <sub>1</sub> * | Q <sub>0</sub> * | State | Q <sub>1</sub> * | Q <sub>0</sub> * | А |

| G01   | 0              | 0              | G00        | 1                | 0                | G10   | 1                | 1                | 1 |

| G11   | 0              | 1              | G01        | 0                | 0                | G11   | 0                | 1                | 0 |

| G10   | 1              | 1              | G01        | 0                | 0                | G11   | 0                | 1                | 1 |

| G00   | 1              | 0              | G00        | 1                | 0                | G10   | 1                | 1                | 0 |

#### **Excitation Table**

The goal is to produce logic for the inputs to the FF's (D<sub>1</sub>, D<sub>0</sub>)...these are the excitation equations

### **Excitation Table**

- Using your transition table you know what you want Q\* to be, but how can you make that happen?

- For D-FF's Q\* will be whatever D is at the edge

#### **Excitation Table**

In a D-FF Q\* will be whatever D is, so if we know what we want Q\* to be just make sure that's what the D input is

| Next State |                |                |                                     |   |   |       |                |                |        |

|------------|----------------|----------------|-------------------------------------|---|---|-------|----------------|----------------|--------|

| Curre      | nt Stat        | е              | S = 0                               |   |   | S = 1 |                |                | Output |

| State      | Q <sub>1</sub> | Q <sub>0</sub> | State D <sub>1</sub> D <sub>0</sub> |   |   | State | D <sub>1</sub> | D <sub>0</sub> | А      |

| G01        | 0              | 0              | G00                                 | 1 | 0 | G10   | 1              | 1              | 1      |

| G11        | 0              | 1              | G01                                 | 0 | 0 | G11   | 0              | 1              | 0      |

| G10        | 1              | 1              | G01                                 | 0 | 0 | G11   | 0              | 1              | 1      |

| G00        | 1              | 0              | G00                                 | 1 | 0 | G10   | 1              | 1              | 0      |

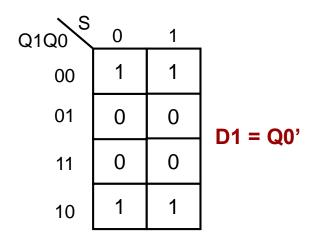

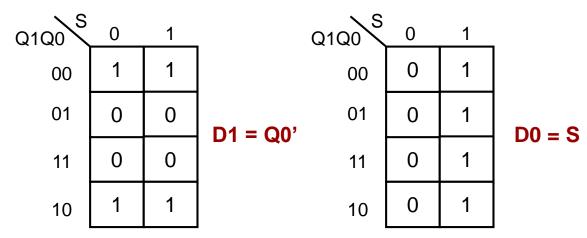

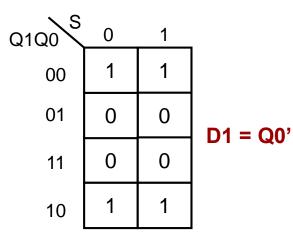

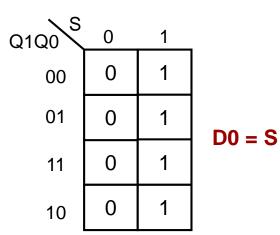

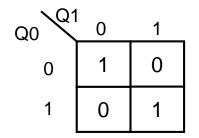

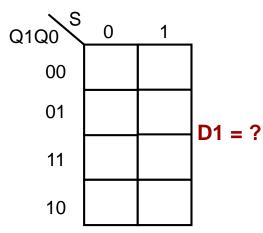

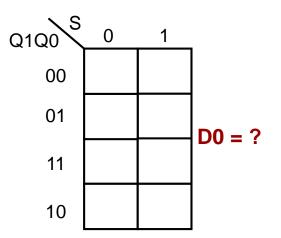

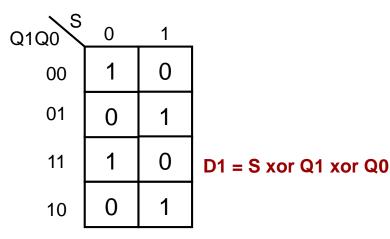

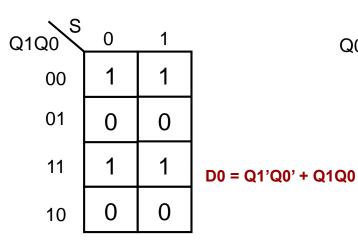

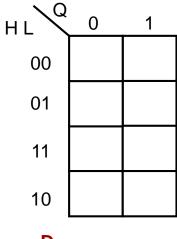

### Karnaugh Maps

• Now need to perform K-Maps for D1, D0, and A

|       | at Cta         | to    |       |                | Next S | tate  |                |       | Output |

|-------|----------------|-------|-------|----------------|--------|-------|----------------|-------|--------|

| Curre | ni Sia         | le    | S     | 5 = 0          |        | S     | = 1            |       | Output |

| State | Q <sub>1</sub> | $Q_0$ | State | D <sub>1</sub> | $D_0$  | State | D <sub>1</sub> | $D_0$ | А      |

| G01   | 0              | 0     | G00   | 1              | 0      | G10   | 1              | 1     | 1      |

| G11   | 0              | 1     | G01   | 0              | 0      | G11   | 0              | 1     | 0      |

| G10   | 1              | 1     | G01   | 0              | 0      | G11   | 0              | 1     | 1      |

| G00   | 1              | 0     | G00   | 1              | 0      | G10   | 1              | 1     | 0      |

### Karnaugh Maps

• Now need to perform K-Maps for D1, D0, and A

|       | at Sta         | to    |       |                | Next S         | tate  |                |                | Output |

|-------|----------------|-------|-------|----------------|----------------|-------|----------------|----------------|--------|

| Curre | ni Sia         | le    | S     | 5 = 0          |                | S     | = 1            |                | Output |

| State | Q <sub>1</sub> | $Q_0$ | State | D <sub>1</sub> | D <sub>0</sub> | State | D <sub>1</sub> | D <sub>0</sub> | А      |

| G01   | 0              | 0     | G00   | 1              | 0              | G10   | 1              | 1              | 1      |

| G11   | 0              | 1     | G01   | 0              | 0              | G11   | 0              | 1              | 0      |

| G10   | 1              | 1     | G01   | 0              | 0              | G11   | 0              | 1              | 1      |

| G00   | 1              | 0     | G00   | 1              | 0              | G10   | 1              | 1              | 0      |

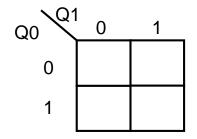

### Karnaugh Maps

• Now need to perform K-Maps for D1, D0, and A

|       | at Cta         | to    |       |                | Next S         | tate  |                |        | Output |

|-------|----------------|-------|-------|----------------|----------------|-------|----------------|--------|--------|

| Curre | ni Sia         | le    | S     | 5 = 0          |                | S     |                | Output |        |

| State | Q <sub>1</sub> | $Q_0$ | State | D <sub>1</sub> | D <sub>0</sub> | State | D <sub>1</sub> | $D_0$  | А      |

| G01   | 0              | 0     | G00   | 1              | 0              | G10   | 1              | 1      | 1      |

| G11   | 0              | 1     | G01   | 0              | 0              | G11   | 0              | 1      | 0      |

| G10   | 1              | 1     | G01   | 0              | 0              | G11   | 0              | 1      | 1      |

| G00   | 1              | 0     | G00   | 1              | 0              | G10   | 1              | 1      | 0      |

$A = Q_1'Q_0' + Q1Q0$  $= Q_1 XNOR Q_0$

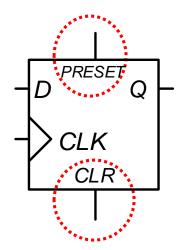

## Implementing the Circuit

• Implements the alternating detector

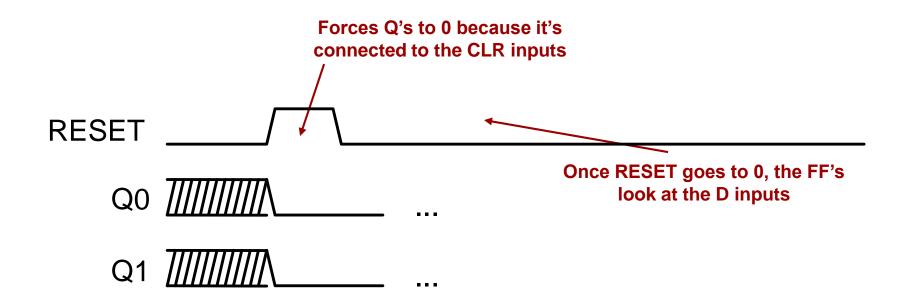

- How can we make the machine start in G0 on reset (or power on?)

- Flip-flops by themselves will initalize to a random state (1 or 0) when power is turned on

- Use the CLEAR and PRESET inputs on our flip-flops in the state memory

- When CLEAR is active the FF initializes Q=0

- When PRESET is active the FF initializes Q=1

We assigned G0 the binary code Q<sub>1</sub>Q<sub>0</sub>=00 so we must initialize our Flip-Flop's to 00

• Use the CLR inputs of your FF's along with the RESET signal to initialize them to 0's

• We don't want to initialize our flip-flops to 1's (only Q1Q0=00) so we just don't use PRE (tie to 'off'='0')

• When RESET is activated Q's initialize to 0 and then when it goes back to 1 the Q's look at the D inputs

### Alternate State Assignment

- Important Fact: The codes we assign to our states can have a big impact on the size of the NSL and OFL

- Let us work again with a different set of assignments

| State | Q <sub>1</sub> | $Q_0$ |

|-------|----------------|-------|

| G01   | 0              | 0     |

| G11   | 0              | 1     |

| G10   | 1              | 1     |

| G00   | 1              | 0     |

**Old Assignments**

| Currer | nt Sta                | ate   |       |     | Next S | tate  |     | Out |

|--------|-----------------------|-------|-------|-----|--------|-------|-----|-----|

| Ourici |                       |       | S     | = 0 |        | S     | = 1 | put |

| State  | <b>Q</b> <sub>1</sub> | $Q_0$ | State |     |        | State |     | А   |

| G01    | 0                     | 0     | G00   |     |        | G10   |     | 1   |

| G10    | 0                     | 1     | G01   |     |        | G11   |     | 1   |

| G00    | 1                     | 1     | G00   |     |        | G10   |     | 0   |

| G11    | 1                     | 0     | G01   |     |        | G11   |     | 0   |

New Assignments

### Alternate State Assignment

| Curre  | nt Stat        | Ā     |       |            | Next S     | tate  |            |            | Output |

|--------|----------------|-------|-------|------------|------------|-------|------------|------------|--------|

| Curren |                | 0     | S     | 6 = 0      |            | S     | = 1        |            | Output |

| State  | Q <sub>1</sub> | $Q_0$ | State | Q1*=<br>D1 | Q0*=<br>D0 | State | Q1*<br>=D1 | Q0*<br>=D0 | А      |

| G01    | 0              | 0     | G00   | 1          | 1          | G10   | 0          | 1          | 1      |

| G10    | 0              | 1     | G01   | 0          | 0          | G11   | 1          | 0          | 1      |

| G00    | 1              | 1     | G00   | 1          | 1          | G10   | 0          | 1          | 0      |

| G11    | 1              | 0     | G01   | 0          | 0          | G11   | 1          | 0          | 0      |

A = ?

### Alternate State Assignment

| Curre | nt Stat        | Ā     |       |            | Next S     | tate  |            |            | Output |

|-------|----------------|-------|-------|------------|------------|-------|------------|------------|--------|

| Ourie |                | C     | S     | 6 = 0      |            | S     | = 1        |            | Output |

| State | Q <sub>1</sub> | $Q_0$ | State | Q1*=<br>D1 | Q0*=<br>D0 | State | Q1*<br>=D1 | Q0*<br>=D0 | А      |

| G01   | 0              | 0     | G00   | 1          | 1          | G10   | 0          | 1          | 1      |

| G10   | 0              | 1     | G01   | 0          | 0          | G11   | 1          | 0          | 1      |

| G00   | 1              | 1     | G00   | 1          | 1          | G10   | 0          | 1          | 0      |

| G11   | 1              | 0     | G01   | 0          | 0          | G11   | 1          | 0          | 0      |

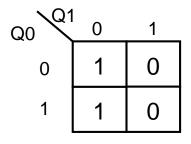

$A = Q_1'$

#### EXAMPLE 2

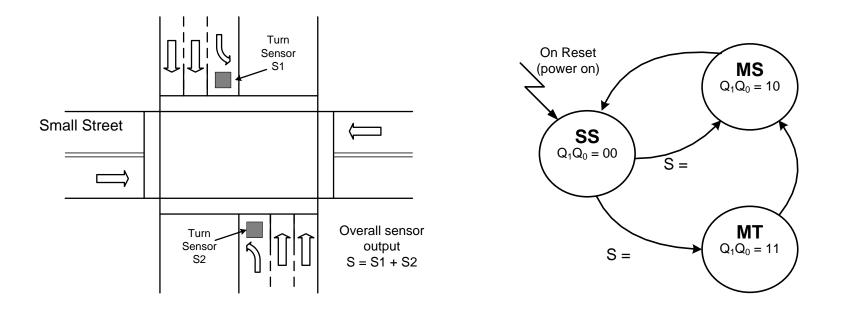

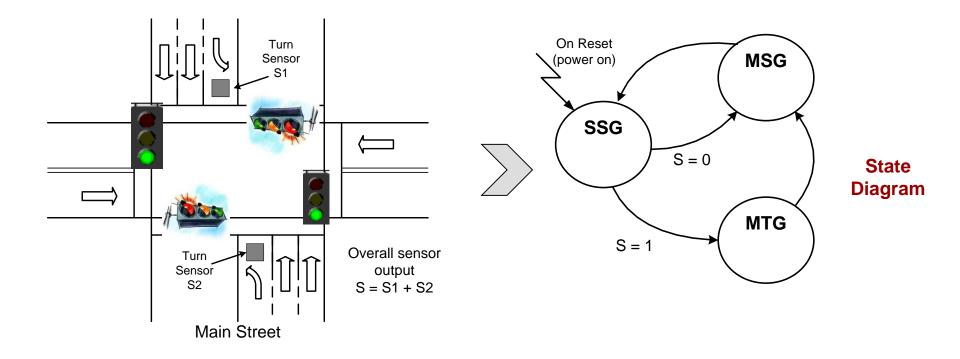

### **Traffic Light Controller**

1-7.51

School of Engineering

- Design the controller for a traffic light at an intersection

- Main street has a protected turn while small street does not

- Sensors embedded in the street to detect cars waiting to turn

- Let S = S1 OR S2 to check if any car is waiting

- Simplify and only have Green and Red lights (no yellow)

### USC Viterbi

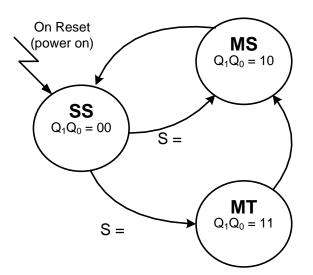

### State Assignment

- Design of the traffic light controller with main turn arrow

- Represent states with some binary code

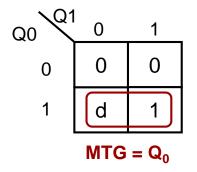

- Codes: 3 States => 2 bit code: 00=SSG, 10=MSG, 11=MTG

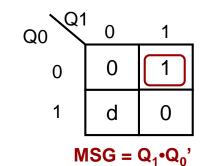

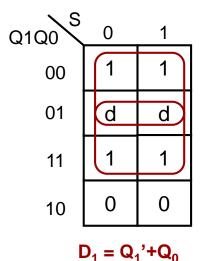

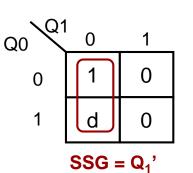

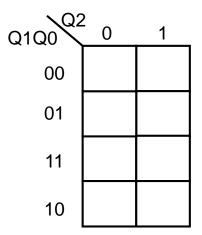

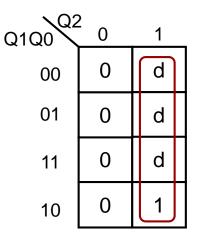

### **K-Maps**

• Find logic for each FF input by using K-Maps

| Cu    | rrer                  | nt             |       | N                       | lext                    | State | ;                       |                         | Output |     |     |  |

|-------|-----------------------|----------------|-------|-------------------------|-------------------------|-------|-------------------------|-------------------------|--------|-----|-----|--|

| St    | tate                  |                | S     | <b>i</b> = <b>0</b>     |                         | S     | 5 = 1                   |                         |        |     |     |  |

| State | <b>Q</b> <sub>1</sub> | Q <sub>0</sub> | State | <b>Q</b> <sub>1</sub> * | <b>Q</b> <sub>0</sub> * | State | <b>Q</b> <sub>1</sub> * | <b>Q</b> <sub>0</sub> * | SSG    | MTG | MSG |  |

| SS    | 0                     | 0              |       |                         |                         |       |                         |                         |        |     |     |  |

| N/A   | 0                     | 1              |       |                         |                         |       |                         |                         |        |     |     |  |

| МТ    | 1                     | 1              |       |                         |                         |       |                         |                         |        |     |     |  |

| MS    | 1                     | 0              |       |                         |                         |       |                         |                         |        |     |     |  |

# K-Maps

1-7.54

School of Engineering

• Find logic for each FF input by using K-Maps

| Cu    | rrer  | nt    |       | N                       | ext     | State | ;                       |         | Output |     |     |  |

|-------|-------|-------|-------|-------------------------|---------|-------|-------------------------|---------|--------|-----|-----|--|

| St    | ate   |       | S     | <b>i</b> = <b>0</b>     |         | S     | 5 = 1                   |         |        |     |     |  |

| State | $Q_1$ | $Q_0$ | State | <b>Q</b> <sub>1</sub> * | $Q_0^*$ | State | <b>Q</b> <sub>1</sub> * | $Q_0^*$ | SSG    | MTG | MSG |  |

| SS    | 0     | 0     | MS    | 1                       | 0       | МТ    | 1                       | 1       | 1      | 0   | 0   |  |

| N/A   | 0     | 1     | х     | d                       | d       | х     | d                       | d       | d      | d   | d   |  |

| МТ    | 1     | 1     | MS    | 1                       | 0       | MS    | 1                       | 0       | 0      | 1   | 0   |  |

| MS    | 1     | 0     | SS    | 0                       | 0       | SS    | 0                       | 0       | 0      | 0   | 1   |  |

### K-Maps

• Find logic for each FF input by using K-Maps

| Cu    | rrer           | nt |       | N                       | ext     | State | ;                       |         |     | Output |     |

|-------|----------------|----|-------|-------------------------|---------|-------|-------------------------|---------|-----|--------|-----|

| St    | State          |    | S     | <b>i</b> = <b>0</b>     |         | S     | 5 = 1                   |         |     | Output |     |

| State | Q <sub>1</sub> | Q₀ | State | <b>Q</b> <sub>1</sub> * | $Q_0^*$ | State | <b>Q</b> <sub>1</sub> * | $Q_0^*$ | SSG | MTG    | MSG |

| SS    | 0              | 0  | MS    | 1                       | 0       | МТ    | 1                       | 1       | 1   | 0      | 0   |

| N/A   | 0              | 1  | х     | d                       | d       | х     | d                       | d       | d   | d      | d   |

| МТ    | 1              | 1  | MS    | 1                       | 0       | MS    | 1                       | 0       | 0   | 1      | 0   |

| MS    | 1              | 0  | SS    | 0                       | 0       | SS    | 0                       | 0       | 0   | 0      | 1   |

1-7.55

School of Engineering

$\begin{array}{c|ccccc} S & 0 & 1 \\ 00 & 0 & 1 \\ 01 & d & d \\ 11 & 0 & 0 \\ 10 & 0 & 0 \\ \end{array}$   $\begin{array}{c} D_0 = S \cdot Q_1' \end{array}$

#### EXAMPLE 3

### USC Viterbi

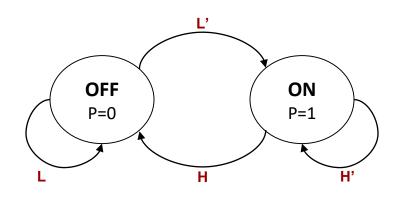

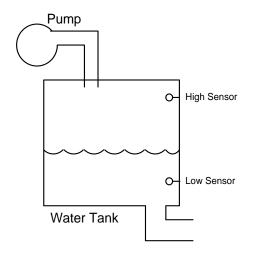

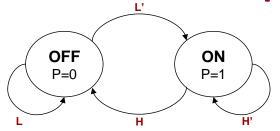

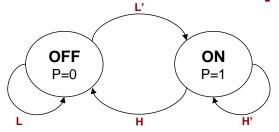

#### Water Pump

• Implement the water pump controller using the High and Low sensors as inputs

### **Transition Table**

| Current Sta | te |           |    | Next State |    |           |    |           |    |  |  |

|-------------|----|-----------|----|------------|----|-----------|----|-----------|----|--|--|

|             |    | H L = 0 0 |    | H L = 0 1  |    | H L = 1 1 |    | H L = 1 0 |    |  |  |

| Symbol      | Q  | Sym.      | Q* | Sym.       | Q* | Sym.      | Q* | Sym.      | Q* |  |  |

| OFF         | 0  |           |    |            |    |           |    |           |    |  |  |

| ON          | 1  |           |    |            |    |           |    |           |    |  |  |

Note: The State Value, Q forms the Pump output (i.e. 1 when we want the pump to be on and 0 othewise)

**D** =

### **Transition Table**

| Current Sta | te | Next State |     |      |    |      |    |           |    |  |  |  |  |

|-------------|----|------------|-----|------|----|------|----|-----------|----|--|--|--|--|

|             |    | H L = (    | 0 0 | HL=  | 01 | HL=  | 11 | H L = 1 0 |    |  |  |  |  |

| Symbol      | Q  | Sym.       | Q*  | Sym. | Q* | Sym. | Q* | Sym.      | Q* |  |  |  |  |

| OFF         | 0  | ON         | 1   | OFF  | 0  | OFF  | 0  | X         | d  |  |  |  |  |

| ON          | 1  | ON 1       |     | ON   | 1  | OFF  | 0  | Х         | d  |  |  |  |  |

Note: The State Value, Q forms the Pump output (i.e. 1 when we want the pump to be on and 0 othewise)

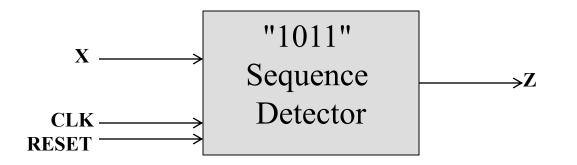

#### EXAMPLE 4

## State Machine Example

- Design a sequence detector to check for the combination "1011"

- Input, X, provides 1-bit per clock

- Check the sequence of X for "1011" in successive clocks

- If "1011" detected, output Z=1 (Z=0 all other times)

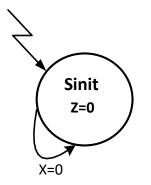

### State Diagram

• Be sure to handle overlapping sequences

### **Transition Output Table**

• Translate the state diagram into the transition output table

| Current State |       |         |    | Next State |     |     |     |        |     |     |     |   |

|---------------|-------|---------|----|------------|-----|-----|-----|--------|-----|-----|-----|---|

|               | urren | l State | :  | X = 0      |     |     |     |        |     | ut  |     |   |

| State         | Q2    | Q1      | Q0 | State*     | Q2* | Q1* | Q0* | State* | Q2* | Q1* | Q0* | Z |

| Sinit         | 0     | 0       | 0  | Sinit      |     |     |     | S1     |     |     |     | 0 |

| S10           | 0     | 0       | 1  | Sinit      |     |     |     | S101   |     |     |     | 0 |

| S1            | 0     | 1       | 1  | S10        |     |     |     | S1     |     |     |     | 0 |

| S101          | 0     | 1       | 0  | S10        |     |     |     | S1011  |     |     |     | 0 |

| S1011         | 1     | 1       | 0  | S10        |     |     |     | S1     |     |     |     | 1 |

### **Transition Output Table**

• Translate the state diagram into the transition output table

| Current State |       |         |    | Next State |     |     |     |        |     |     |     |   |

|---------------|-------|---------|----|------------|-----|-----|-----|--------|-----|-----|-----|---|

|               | urren | l State | •  | X = 0      |     |     |     |        |     | ut  |     |   |

| State         | Q2    | Q1      | Q0 | State*     | Q2* | Q1* | Q0* | State* | Q2* | Q1* | Q0* | Z |

| Sinit         | 0     | 0       | 0  | Sinit      | 0   | 0   | 0   | S1     | 0   | 1   | 1   | 0 |

| S10           | 0     | 0       | 1  | Sinit      | 0   | 0   | 0   | S101   | 0   | 1   | 0   | 0 |

| S1            | 0     | 1       | 1  | S10        | 0   | 0   | 1   | S1     | 0   | 1   | 1   | 0 |

| S101          | 0     | 1       | 0  | S10        | 0   | 0   | 1   | S1011  | 1   | 1   | 0   | 0 |

| S1011         | 1     | 1       | 0  | S10        | 0   | 0   | 1   | S1     | 0   | 1   | 1   | 1 |

### **Transition Output Table**

• Translate the state diagram into the transition output table

| Current State |       |         |    | Next State |    |    |    |        |    |    |    |   |

|---------------|-------|---------|----|------------|----|----|----|--------|----|----|----|---|

|               | urren | l State | •  | X = 0      |    |    |    |        |    | ut |    |   |

| State         | Q2    | Q1      | Q0 | State*     | D2 | D1 | D0 | State* | D2 | D1 | D0 | Z |

| Sinit         | 0     | 0       | 0  | Sinit      | 0  | 0  | 0  | S1     | 0  | 1  | 1  | 0 |

| S10           | 0     | 0       | 1  | Sinit      | 0  | 0  | 0  | S101   | 0  | 1  | 0  | 0 |

| S1            | 0     | 1       | 1  | S10        | 0  | 0  | 1  | S1     | 0  | 1  | 1  | 0 |

| S101          | 0     | 1       | 0  | S10        | 0  | 0  | 1  | S1011  | 1  | 1  | 0  | 0 |

| S1011         | 1     | 1       | 0  | S10        | 0  | 0  | 1  | S1     | 0  | 1  | 1  | 1 |

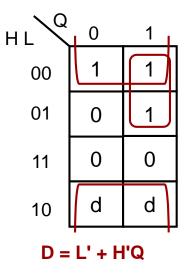

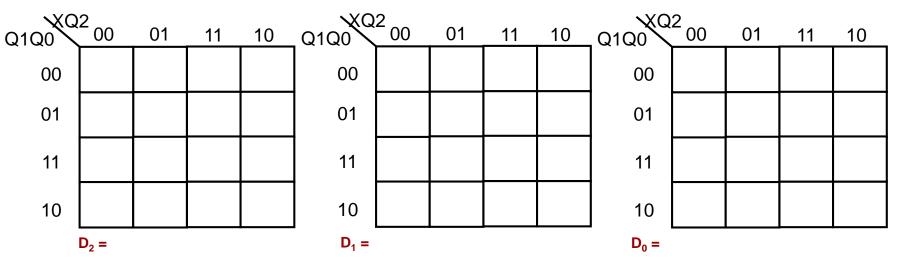

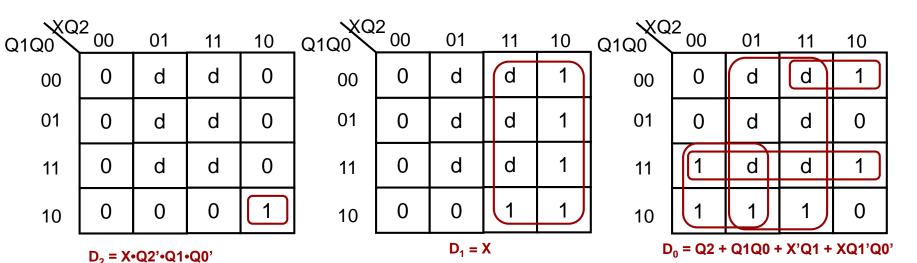

### NSL & OFL

|       | urren | 4 6404 | •  | Next State |    |    |    |        |     |    |    |   |

|-------|-------|--------|----|------------|----|----|----|--------|-----|----|----|---|

|       | unen  | i Stat | e  | X = 0      |    |    |    |        | put |    |    |   |

| State | Q2    | Q1     | Q0 | State*     | D2 | D1 | D0 | State* | D2  | D1 | D0 | Z |

| Sinit | 0     | 0      | 0  | Sinit      | 0  | 0  | 0  | S1     | 0   | 1  | 1  | 0 |

| S10   | 0     | 0      | 1  | Sinit      | 0  | 0  | 0  | S101   | 0   | 1  | 0  | 0 |

| S1    | 0     | 1      | 1  | S10        | 0  | 0  | 1  | S1     | 0   | 1  | 1  | 0 |

| S101  | 0     | 1      | 0  | S10        | 0  | 0  | 1  | S1011  | 1   | 1  | 0  | 0 |

| S1011 | 1     | 1      | 0  | S10        | 0  | 0  | 1  | S1     | 0   | 1  | 1  | 1 |

Z =

### NSL & OFL

|       | urren | 4 6404 | •  | Next State |    |    |    |        |     |    |    |   |

|-------|-------|--------|----|------------|----|----|----|--------|-----|----|----|---|

|       | unen  | i Stat | e  | X = 0      |    |    |    |        | put |    |    |   |

| State | Q2    | Q1     | Q0 | State*     | D2 | D1 | D0 | State* | D2  | D1 | D0 | Z |

| Sinit | 0     | 0      | 0  | Sinit      | 0  | 0  | 0  | S1     | 0   | 1  | 1  | 0 |

| S10   | 0     | 0      | 1  | Sinit      | 0  | 0  | 0  | S101   | 0   | 1  | 0  | 0 |

| S1    | 0     | 1      | 1  | S10        | 0  | 0  | 1  | S1     | 0   | 1  | 1  | 0 |

| S101  | 0     | 1      | 0  | S10        | 0  | 0  | 1  | S1011  | 1   | 1  | 0  | 0 |

| S1011 | 1     | 1      | 0  | S10        | 0  | 0  | 1  | S1     | 0   | 1  | 1  | 1 |

### Drawing the Circuit

### Waveform for 1011 Detector