#### Axioms

**USC** Viterbi

**USC**Viter

- Axioms are the basis for Boolean Algebra

- Notice that these axioms are simply restating our definition of digital/binary logic

- A1/A1' = Binary variables (only 2 values possible)

- A2/A2' = NOT operation

- A3,A4,A5 = AND operation

- A3',A4',A5' = OR operation

| (A1) | X = 0 if X ≠ 1              | (A1') | X = 1 if X ≠ 0             |

|------|-----------------------------|-------|----------------------------|

| (A2) | If $X = 0$ , then $X' = 1$  | (A2') | If $X = 1$ , then $X' = 0$ |

| (A3) | $0 \bullet 0 = 0$           | (A3') | 1 + 1 = 1                  |

| (A4) | 1 • 1 = 1                   | (A4') | 0 + 0 = 0                  |

| (A5) | $1 \cdot 0 = 0 \cdot 1 = 0$ | (A5') | 0 + 1 = 1 + 0 = 1          |

# Duality

• The "dual" of an expression is not equal to the original

$\begin{array}{ccc}1+0\\ & \neq \\ \text{Original}\\ \text{expression}\end{array} \end{array} \neq \begin{array}{ccc}0 \bullet 1\\ & \text{Dual}\end{array}$

Taking the "dual" of both sides of an equation yields a new equation

USC Viter

### Duality

- Every truth statement can yields another truth statement

- I exercise if I have time <u>and</u> energy (original statement)

- I don't exercise if I don't have time <u>or</u> don't have energy (dual statement)

- To express the dual, swap...

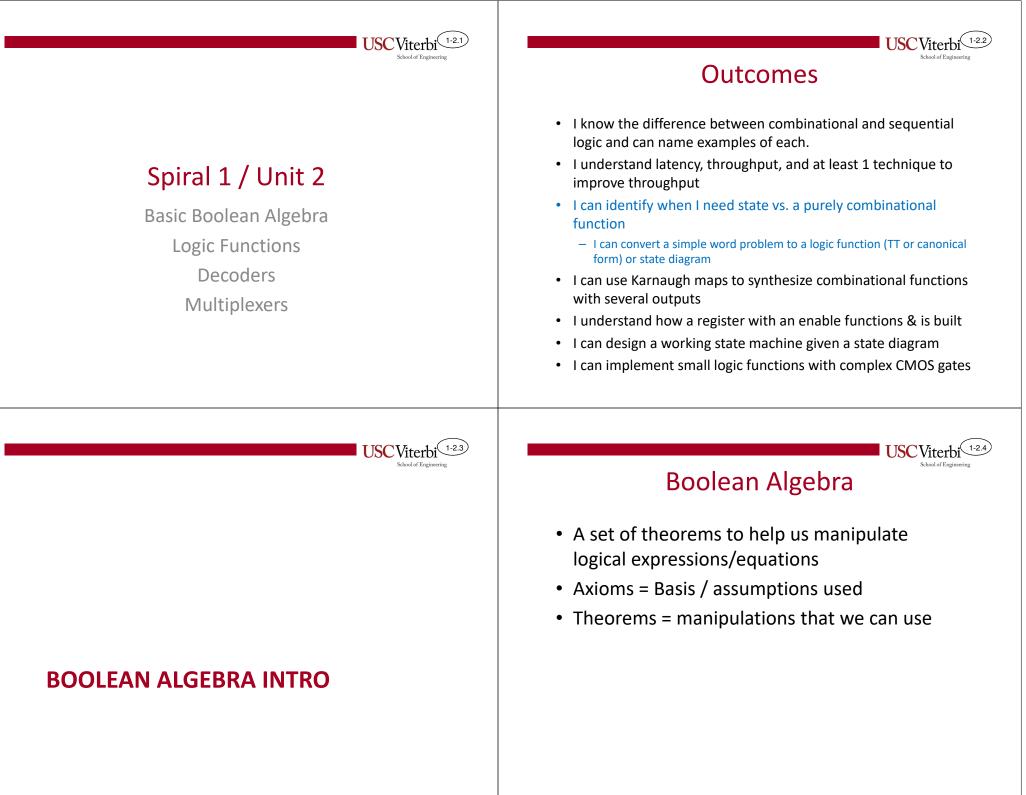

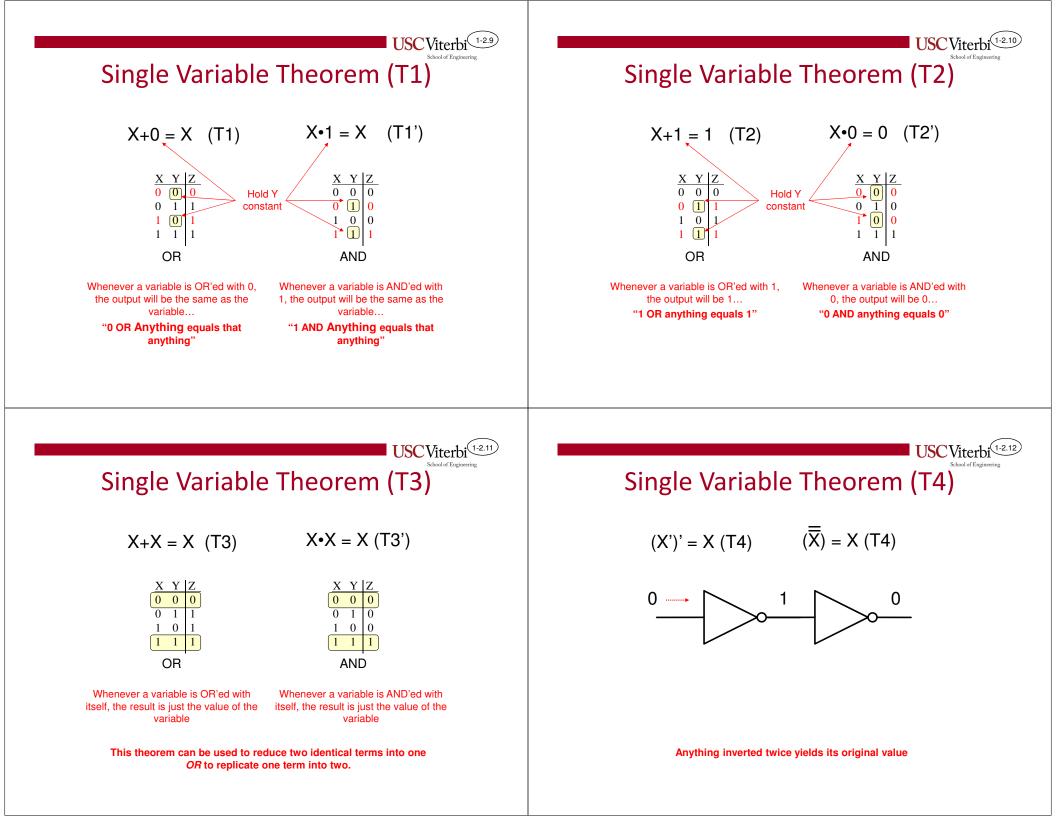

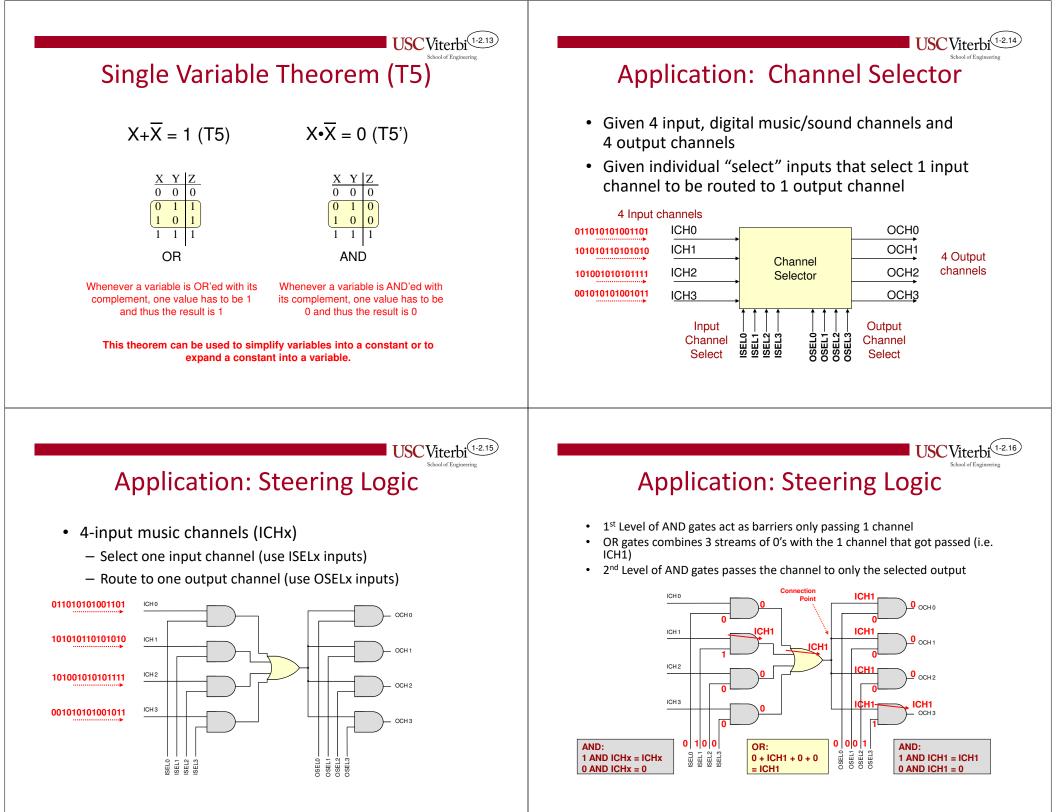

## Single Variable Theorems

- Provide some simplifications for expressions containing:

- a single variable

- a single variable and a constant bit

- Each theorem has a dual (another true statement)

- Each theorem can be proved by writing a truth table for both sides (i.e. proving the theorem holds for all possible values of X)

| T1 | X + 0 = X  | T1' | X • 1 = X         |

|----|------------|-----|-------------------|

| Т2 | X + 1 = 1  | T2' | X • 0 = 0         |

| Т3 | X + X = X  | Т3' | $X \bullet X = X$ |

| Т4 | (X')' = X  |     |                   |

| T5 | X + X' = 1 | T5' | X • X' = 0        |

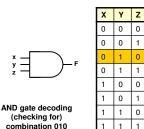

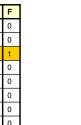

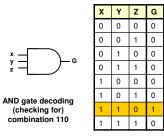

### Checkers / Decoders

- Place inverters at the input of the AND gates such that

- F produces '1' only for input combination  $\{x,y,z\} = \{010\}$

- G produces '1' only for input combination  $\{x,y,z\} = \{110\}$

An OR gate only outputs '0' for 1 combination

That combination can be changed by adding inverters to the inputs

0

0

combination 110

School of Fr

**USC**Viterbi

USC Viterbi

School of Engineer

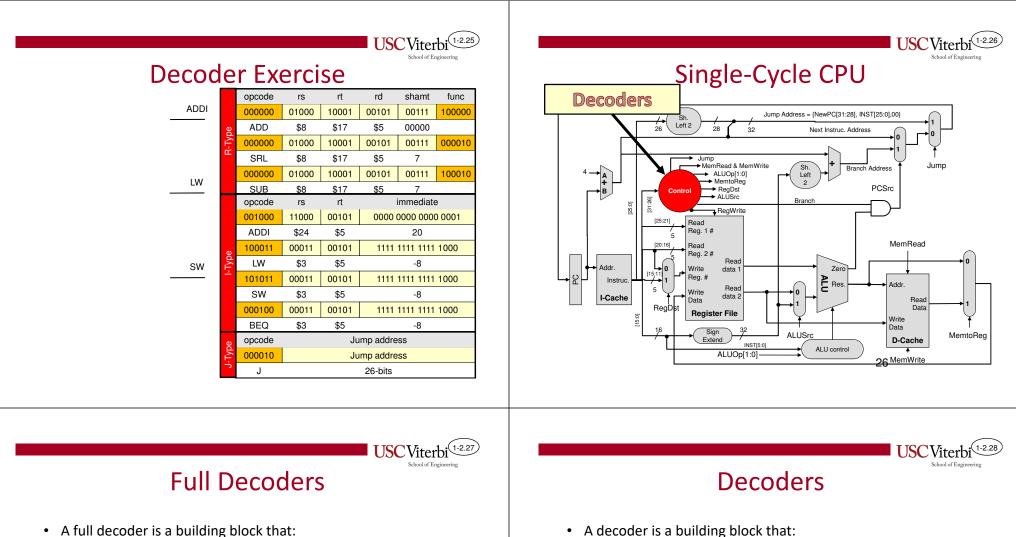

#### **Decoder Exercise**

Design an instruction decoder that uses opcode[5:0] and func[5:0] as inputs and produces a separate output {ADD, SRL, SUB, etc.} for each instruction type that will produce '1' when that instruction is loaded

| R-Type | opcode | rs           | rt    | rd                  | shamt | func   |  |  |

|--------|--------|--------------|-------|---------------------|-------|--------|--|--|

|        | 000000 | 01000        | 10001 | 00101               | 00111 | 100000 |  |  |

|        | ADD    | \$8          | \$17  | \$5                 | 00000 |        |  |  |

|        | 000000 | 01000        | 10001 | 00101               | 00111 | 000010 |  |  |

|        | SRL    | \$8          | \$17  | \$5                 | 7     |        |  |  |

|        | 000000 | 01000        | 10001 | 00101               | 00111 | 100010 |  |  |

|        | SUB    | \$8          | \$17  | \$5 7               |       |        |  |  |

| I-Type | opcode | rs           | rt    | immediate           |       |        |  |  |

|        | 001000 | 11000        | 00101 | 0000 0000 0000 0001 |       |        |  |  |

|        | ADDI   | \$24         | \$5   | 20                  |       |        |  |  |

|        | 100011 | 00011        | 00101 | 1111 1111 1111 1000 |       |        |  |  |

|        | LW     | \$3          | \$5   | -8                  |       |        |  |  |

|        | 101011 | 00011        | 00101 | 1111 1111 1111 1000 |       |        |  |  |

|        | SW     | \$3          | \$5   | -8                  |       |        |  |  |

|        | 000100 | 00011        | 00101 | 1111 1111 1111 1000 |       |        |  |  |

|        | BEQ    | \$3          | \$5   | -8                  |       |        |  |  |

| J-Type | opcode | Jump address |       |                     |       |        |  |  |

|        | 000010 | Jump address |       |                     |       |        |  |  |

| Ļ      | J      | 26-bits      |       |                     |       |        |  |  |

**Decoder Exercise**

|      | _             |                                                                           | <u> </u>                                      |                                                           |                                                      |                                                                    |              |

|------|---------------|---------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------|--------------|

| ADD  | R-Type        | opcode                                                                    | rs                                            | rt                                                        | rd                                                   | shamt                                                              | func         |

|      |               | 000000                                                                    | 01000                                         | 10001                                                     | 00101                                                | 00111                                                              | 100000       |

|      |               | ADD                                                                       | \$8                                           | \$17                                                      | \$5                                                  | 00000                                                              |              |

|      |               | 000000                                                                    | 01000                                         | 10001                                                     | 00101                                                | 00111                                                              | 000010       |

|      |               | SRL                                                                       | \$8                                           | \$17                                                      | \$5                                                  | 7                                                                  |              |

| 0.51 |               | 000000                                                                    | 01000                                         | 10001                                                     | 00101                                                | 00111                                                              | 100010       |

| SRL  |               | SUB                                                                       | \$8                                           | \$17                                                      | \$5                                                  | 7                                                                  |              |

|      | I-Type        | opcode                                                                    | rs                                            | rt                                                        | immediate                                            |                                                                    |              |

|      |               | 001000                                                                    | 11000                                         | 00101                                                     | 0000 0000 0000 0001                                  |                                                                    |              |

|      |               | ADDI                                                                      | \$24                                          | \$5                                                       | 20                                                   |                                                                    |              |

|      |               | 100011                                                                    | 00011                                         | 00101                                                     | 1111                                                 | 1111 1111                                                          | 1000         |

| SUB  |               | LW                                                                        | \$3                                           | \$5                                                       | -8                                                   |                                                                    |              |

|      |               | 101011                                                                    | 00011                                         | 00101                                                     | 1111                                                 | 1111 1111                                                          | 1000         |

|      |               | SW                                                                        | \$3                                           | \$5                                                       | -8                                                   |                                                                    |              |

|      |               | 000100                                                                    | 00011                                         | 00101                                                     | 1111 1111 1111 1000                                  |                                                                    |              |

|      |               | BEQ                                                                       | \$3                                           | \$5                                                       |                                                      | -8                                                                 |              |

|      | e             | opcode                                                                    | Jump address                                  |                                                           |                                                      |                                                                    |              |

|      | Typ           | 000010                                                                    | Jump address                                  |                                                           |                                                      |                                                                    |              |

|      | ŀ             | J                                                                         |                                               |                                                           | 26-bits                                              |                                                                    |              |

| SUB  | J-Type I-Type | ADDI<br>100011<br>LW<br>101011<br>SW<br>000100<br>BEQ<br>0pcode<br>000010 | \$24<br>00011<br>\$3<br>00011<br>\$3<br>00011 | \$5<br>00101<br>\$5<br>00101<br>\$5<br>00101<br>\$5<br>Ju | 1111<br>1111<br>1111<br>1111<br>mp addre<br>mp addre | 20<br>1111 1111<br>-8<br>1111 1111<br>-8<br>11111 1111<br>-8<br>ss | 1000<br>1000 |

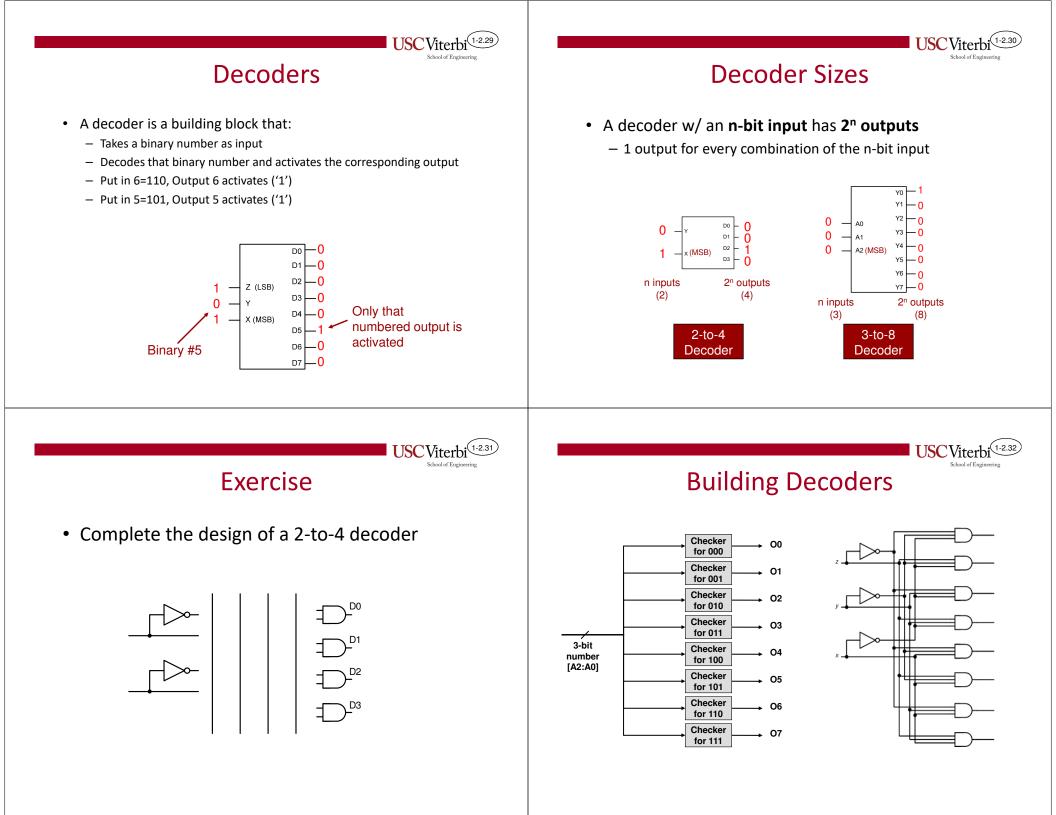

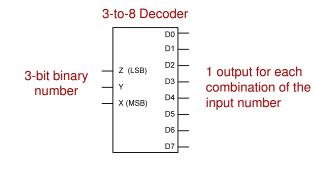

- Takes in an n-bit binary number as input

- Decodes that binary number and activates the corresponding output

- Individual outputs for EVERY (MOST) input combination (i.e. 2<sup>n</sup> outputs)

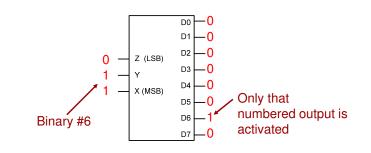

- A decoder is a building block that:

- Takes a binary number as input

- Decodes that binary number and activates the corresponding output

- Put in 6=110, Output 6 activates ('1')

- Put in 5=101, Output 5 activates ('1')