## EE 209 Spiral 1 Exam

| Name: |  |

|-------|--|

|       |  |

- 1.) Answer the following questions as True or False

- a.) A 4-to-1 multiplexer requires at least 4 select lines: true / false

- b.) An 8-to-1 mux and no other logi can be used to implement any combinational logic function of 4 input variables: **true / false**

- c.) A 3-to-8 decoder along with (4) 8-input OR gates can be used to implement any combinational logic involving 3 input variables and 4 output variables: **true / false**

- d.) 3 separate 2-to-1 muxes can be used to build a single 4-to-1 mux: true / false

- e.) 5 flip-flops are <u>required</u> to implement a state machine with 5 states: **true / false**

- f.) In a state machine with Moore style outputs, a change in the external inputs can independently and immediately cause the outputs to change: **true** / **false**

- g.) What are the three primary design goals that we try to optimize in circuit design?

- h.) Given a 5-to-32 decoder with inputs (A4, A3, A2, A1, A0), write out the logic equation for output 17 (i.e. O17)?

- i.) A 20-to-1 mux would require a minimum of how many select bits?

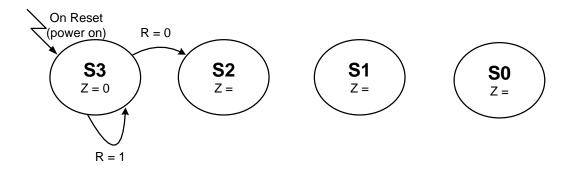

2.) State Machine Design (Down Counter w/ Restart): Design a synchronous state machine circuit that implements a 2-bit down counter (i.e. counts 11, 10, 01, 00, 11...). The circuit has an external input, R (RESTART), that when '1' should force the counter back to the 11 state no matter what the current state is. As long as R stays '1', the counter should stay in the 11 state. The circuit should also have one output Z. Z=1 when in the 00 state and Z=0 otherwise.

Let us use 4 states:

| S3 (initial state on reset) | The count should be $11_2 = 3_{10}$ |

|-----------------------------|-------------------------------------|

| S2                          | The count should be $10_2 = 2_{10}$ |

| S1                          | The count should be $01_2 = 1_{10}$ |

| S0                          | The count should be $00_2 = 0_{10}$ |

a.) Complete the state diagram below by filling in all necessary transitions **and** the values of Z.

- b.) What is the minimum number of flip-flops required to implement this state machine?

- c.) Complete the state transition/output table given below. (Note: We have provided the state assignment already). We have ordered the states in such a way to use gray code ordering, so take care when translating your state diagram to the transition/output table.

| Current State |          | Next State |            |       |            | Output |

|---------------|----------|------------|------------|-------|------------|--------|

|               |          | R=0        |            | F     | R=1        |        |

| State         | $Q_1Q_0$ | State      | $Q_1*Q_0*$ | State | $Q_1*Q_0*$ | Z      |

| S0            | 0.0      |            |            |       |            |        |

| S1            | 0 1      |            |            |       |            |        |

| S3            | 1 1      |            |            |       |            |        |

| S2            | 1 0      |            |            |       |            |        |

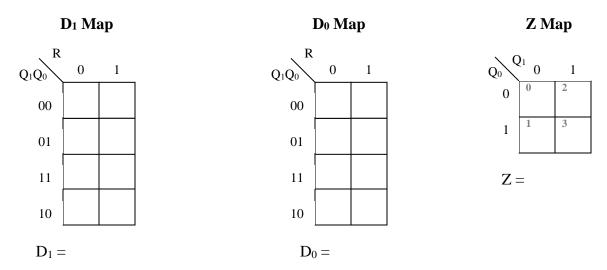

d.) Assume we will implement our circuit using D Flip-Flops. Use the K-Maps below to find minimal expressions for D1, D0, and Z.

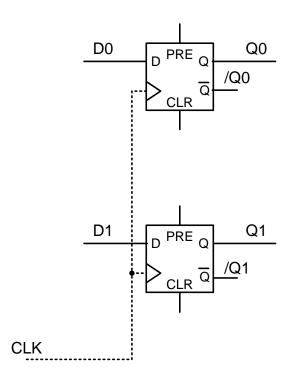

e.) Show how to implement the initial state (power-on/reset state) by connecting the PRE (PRESET) and CLR inputs of the FF's appropriately. Assume the signal RESET is available to you. You do not need to implement the next-state or output-function logic.

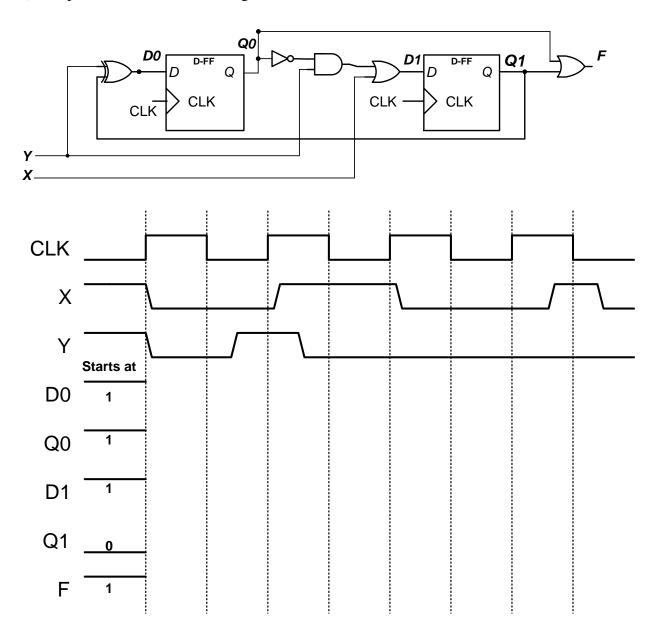

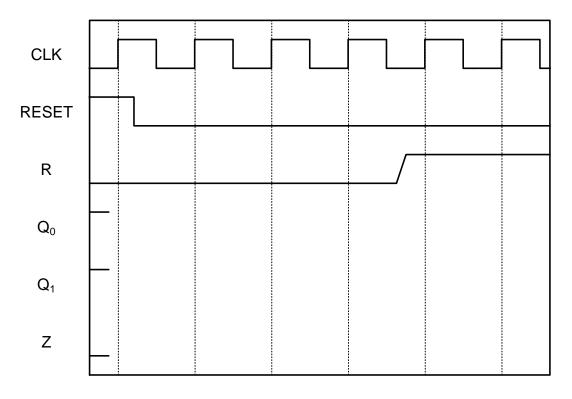

f.) Using your design above draw the waveform for the sequence of states that the machine will go through and what the output will be for the given input sequence of X. Remember you are using <u>positive edge-triggered</u> devices.

$$F = \overline{[(\overline{A} + C) \bullet \overline{B} + (\overline{A} + C) \bullet \overline{C}]} + AB\overline{C}$$

| Single- | Variable Theorems                             |        |                                                     |                  |  |

|---------|-----------------------------------------------|--------|-----------------------------------------------------|------------------|--|

| (T1)    | X + 0 = X                                     | (T1')  | $X \cdot 1 = X$                                     | (Identities)     |  |

| (T2)    | X + 1 = 1                                     | (T2')  | $X \bullet 0 = 0$                                   | (Null elements)  |  |

| (T3)    | X + X = X                                     | (T3')  | $X \bullet X = X$                                   | (Idempotency)    |  |

| (T4)    | (X')' = X                                     |        |                                                     | (Involution)     |  |

| (T5)    | X + X' = 1                                    | (T5')  | $X \cdot X' = 0$                                    | (Complement)     |  |

| Two- ar | nd Three-Variable Theoren                     | ıs     |                                                     |                  |  |

| (T6)    | X + Y = Y + X                                 | (T6')  | $X \bullet Y = Y \bullet X$                         | (Commutativity)  |  |

| (T7)    | (X+Y)+Z=X+(Y+Z)                               | (T7')  | $(X \bullet Y) \bullet Z = X \bullet (Y \bullet Z)$ | (Associativity)  |  |

| (T8)    | $X \bullet (Y+Z) = X \bullet Y + X \bullet Z$ | (T8')  | $X+(Y \bullet Z) = (X+Y) \bullet (X+Z)$             | (Distributivity) |  |

| (T9)    | $X + X \cdot Y = X$                           | (T9')  | $X \bullet (X + Y) = X$                             | (Covering)       |  |

| (T10)   | $X \bullet Y + X \bullet Y' = X$              | (T10') | $(X+Y) \cdot (X+Y') = X$                            | (Combining)      |  |

| (T11)   | $X \bullet Y + X' \bullet Z + Y \bullet Z =$  | (T11') | $(X+Y) \bullet (X'+Z) \bullet (Y+Z) =$              | (Consensus)      |  |

|         | $X \bullet Y + X'Z$ $(X+Y) \bullet (X'+Z)$    |        |                                                     |                  |  |

| DeMorg  | gan's Theorem                                 |        |                                                     |                  |  |

|         | $(X \bullet Y)' = X' + Y'$                    | (T6')  | $(X+Y)' = X' \cdot Y'$                              | (DeMorgan's)     |  |

| <ol> <li>Design a circuit takes a 2-bit, unsigned number A=(A<sub>1</sub>A<sub>0</sub>) and a 1-bit, unsigned in B=(B<sub>0</sub>) as input and produces the output C = A – B represented in the 2's comple system. pts.)</li> </ol>                           |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <ul> <li>a.) Complete the block diagram of this circuit by showing and labeling the inputs and<br/>outputs. Think how many output bits are required.<br/>pts.)</li> </ul>                                                                                      | d (2 |

|                                                                                                                                                                                                                                                                |      |

| b.) Write out a truth table for this circuit. pts.)                                                                                                                                                                                                            | (8   |

|                                                                                                                                                                                                                                                                |      |

|                                                                                                                                                                                                                                                                |      |

|                                                                                                                                                                                                                                                                |      |

|                                                                                                                                                                                                                                                                |      |

|                                                                                                                                                                                                                                                                |      |

| c.) Find the minimal <u>SOP</u> expression for each bit of output by using the 3 K-Maps furthelow. Make sure to add the variable labels for the axes of each K-Map and add your code. Clearly indicate the minimal expressions you find for each output. pts.) |      |

|                                                                                                                                                                                                                                                                |      |

|                                                                                                                                                                                                                                                                |      |

## 5.) Complete the waveform for the given circuit