| USC Viterbi 14.5                                                                                                                                                                                                                                                                            | USC Viterbi 14.6                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

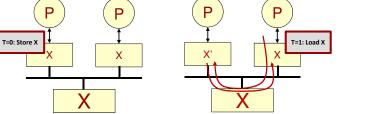

| Snoopy or Snoopy                                                                                                                                                                                                                                                                            | Solving Cache Coherency                                                                                                                                                                                                                                                                                                     |

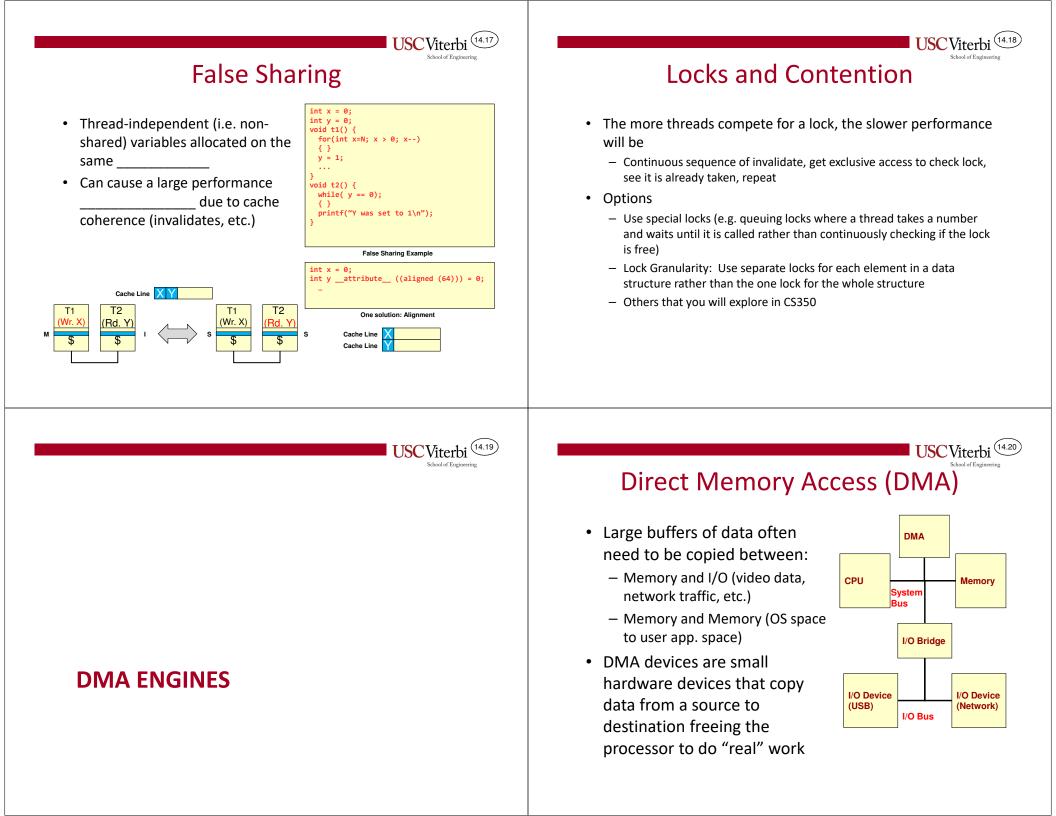

|                                                                                                                                                                                                                                                                                             | <ul> <li>If no writes, multiple copies are fine</li> <li>Two options: When a block is modified <ul> <li></li></ul></li></ul>                                                                                                                                                                                                |

| USC Viterbi<br>School of Engineering                                                                                                                                                                                                                                                        | USC Viterbi<br>School of Engineering<br>Write Back Cache Coherency Protocols                                                                                                                                                                                                                                                |

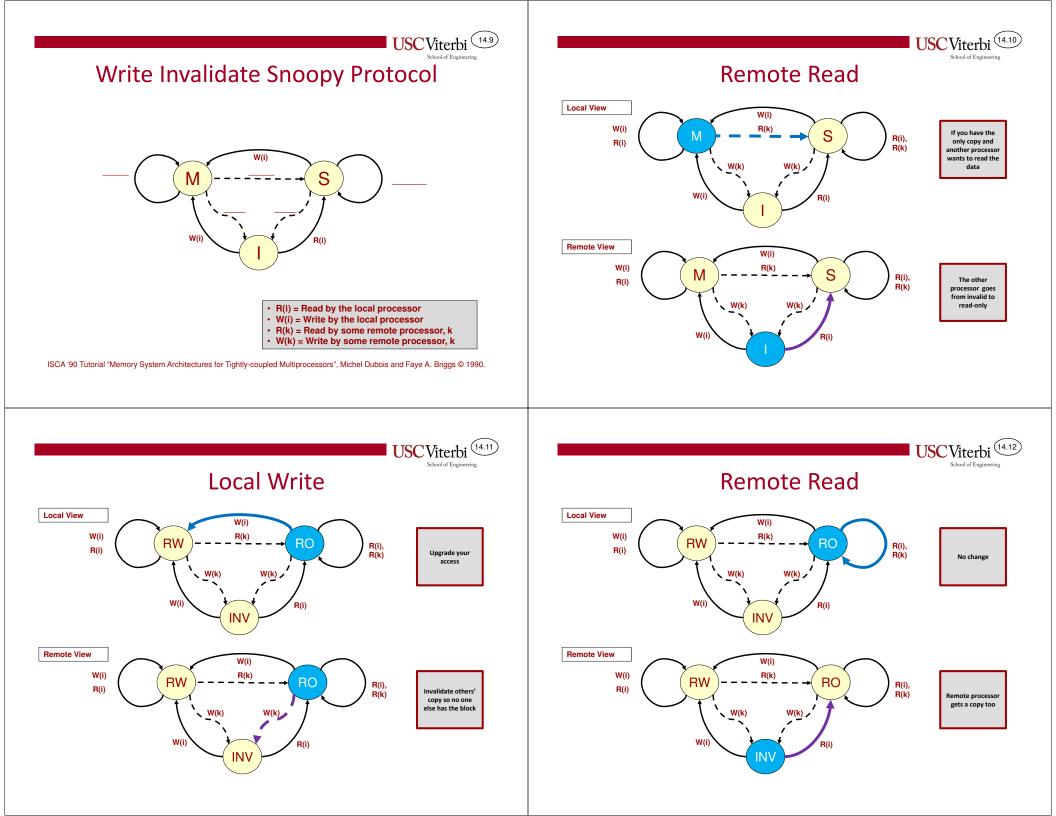

| <ul> <li>A memory system is coherent if the value returned on a Load instruction is always the value given by the instruction by any processor to the same address</li> <li>To implement this ability we need a protocol (set of rules) to track the "state" of each cache block</li> </ul> | <ul> <li>Write invalidate protocols ("Ownership Protocols")</li> <li>Basic 3-state (MSI) Protocol <ul> <li>I =: Not in cache or invalidated earlier</li> <li>RO (Read-Only) =: Processors has a valid block but so might other caches. Thus it is only safe to read their copy (but not write to it)</li> </ul> </li> </ul> |

|                                                                                                                                                                                                                                                                                             | – BW (Read-Write) = : Processors has modified (written)                                                                                                                                                                                                                                                                     |

RW (Read-Write) = \_\_\_\_: Processors has modified (written) to the block and it is guaranteed to have the only copy (no other caches have a copy). Thus it is only safe to read or write.

ISCA '90 Tutorial "Memory System Architectures for Tightly-coupled Multiprocessors", Michel Dubois and Faye A. Briggs © 1990.

USCViterbi (14.13)

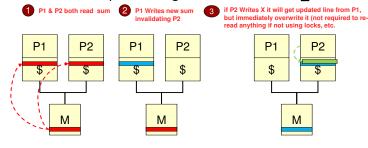

## Coherency Example

| Processor<br>Activity  | P1 \$<br>Content | P1 Block<br>State<br>(M,S,I) | P2 \$<br>Content | P2 Block<br>State<br>(M,S,I) | Memory<br>Contents |

|------------------------|------------------|------------------------------|------------------|------------------------------|--------------------|

|                        | -                | -                            | -                | -                            | А                  |

| P1 reads<br>block X    |                  |                              |                  |                              |                    |

| P2 reads<br>block X    |                  |                              |                  |                              |                    |

| P1 writes<br>block X=B |                  |                              |                  |                              |                    |

| P2 reads<br>block X    |                  |                              |                  |                              |                    |

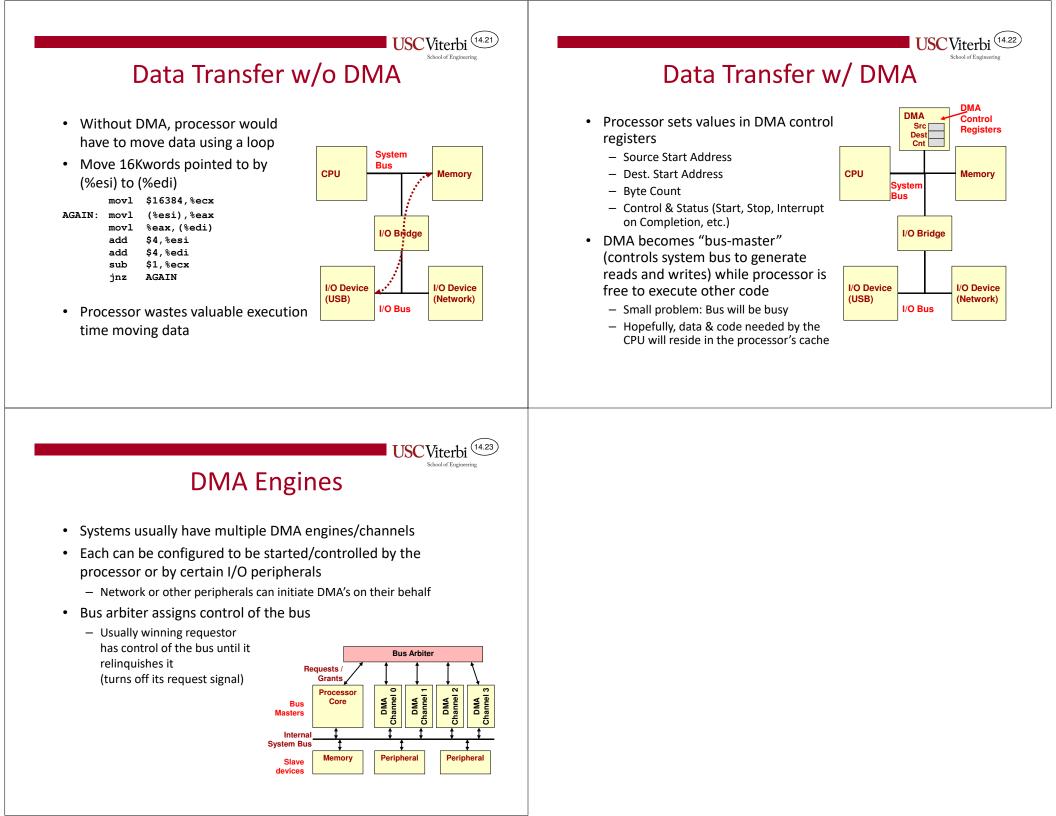

## Another Coherency Example

USC Viterbi (14.14)

USC Viterbi (14.16)

| Processor<br>Activity | P1 \$<br>Content | P1 Block<br>State<br>(M,S,I) | P2 \$<br>Content | P2 Block<br>State<br>(M,S,I) | Memory<br>Contents |

|-----------------------|------------------|------------------------------|------------------|------------------------------|--------------------|

|                       | -                | -                            | -                | -                            | А                  |

| P1 reads<br>block X   |                  |                              |                  |                              |                    |

| P1 writes<br>X=B      |                  |                              |                  |                              |                    |

| P2 writes<br>X=C      |                  |                              |                  |                              |                    |

| P1 reads<br>block X   |                  |                              |                  |                              |                    |

USC Viterbi

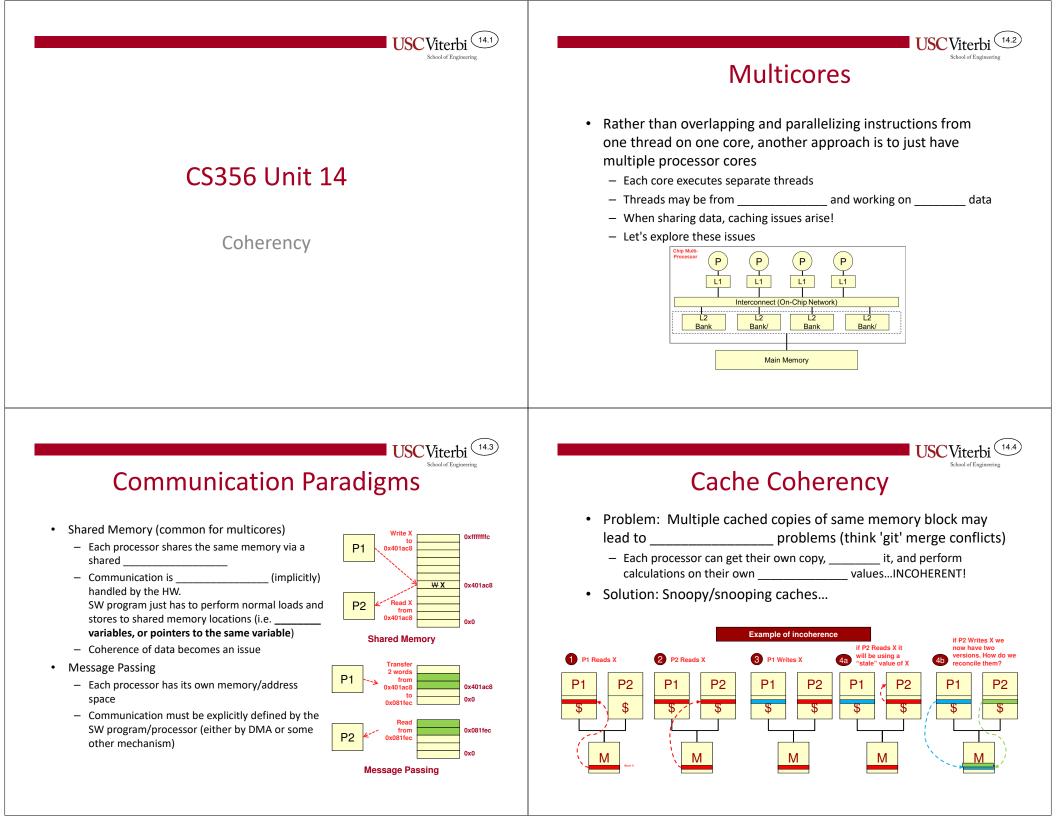

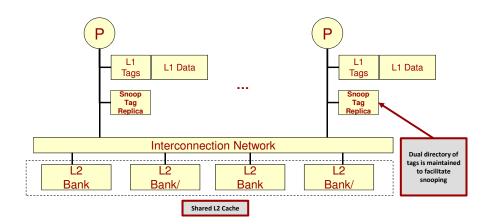

## **Coherence Implementation**

## Is Cache Coherency = Atomicity?

- Does coherency take the place of locking/synchronization?

- \_\_\_\_, cache coherence only serializes \_\_\_\_\_\_ and does not serialize entire \_\_\_\_\_\_ sequences

Coherence simply ensures two processors don't read two different values of the same memory location

• Consider two threads performing: sum += thread val